14nm之后,再说什么几nm,往往都是数字游戏了,用晶体管密度来测定更合理 既然如此有人说麒麟9100预计晶体管数量在140亿左右,再看看台积电5nm能做到170亿,所以有人说麒麟9100相当于5.5nm倒也说得过去,但同时也要知道5.5nm和5nm这个坎没有那么容易过去。 所以就目前的情况来看,传闻中的麒麟9100工艺密度应该快到国内的极限了,这的确非常厉害,但后续怎么办也是个问题,最近老美那边疯了,准备下狠手,要卡得更紧了

14nm之后,再说什么几nm,往往都是数字游戏了,用晶体管密度来测定更合理 既然如此有人说麒麟9100预计晶体管数量在140亿左右,再看看台积电5nm能做到170亿,所以有人说麒麟9100相当于5.5nm倒也说得过去,但同时也要知道5.5nm和5nm这个坎没有那么容易过去。 所以就目前的情况来看,传闻中的麒麟9100工艺密度应该快到国内的极限了,这的确非常厉害,但后续怎么办也是个问题,最近老美那边疯了,准备下狠手,要卡得更紧了

评论列表

作者最新文章

热门分类

科技TOP

科技最新文章

用户17xxx15

国产EUV2023年底已经在长光所整合出样机了,华为是第一批介入EUV调试运转的企业,今年下半年华为已经可以明确推出5纳米芯片,传闻是DUV四重曝光和EUV两种工艺混搭生产,而且DUV模式下5纳米也不是中芯国际做的

风行水上 回复 07-19 15:22

你这消息是自己的臆想吗

用户17xxx15 回复 风行水上 07-19 18:29

部分消息已经公布,你是文盲吧

。。。

duv的5nm支撑一两年就够了,国产euv也快了。5nm工艺也可以不断改良提升性能,就像英特尔初代10nm改进了三四代不也有性能改进么。

paulyellow 回复 07-19 08:59

还没得很,良率很低

用户10xxx32 回复 07-19 23:42

相同工艺下的提升性能只能是改进芯片设计。相同工艺下的制造是提升良品率,哪怕提升千分之一都是相当不错。又或改进生产工艺,降低成本或提高良品率。

雅蠛蝶是什么蝶

老美真是明灯啊,卡什么突破什么!甚至都不用自己规划接下来突破的重点[抠鼻]

看潮者 回复 07-19 12:06

有前人走成功了的路,后人死扣这个方向,总能出来,而自己规划未知方向,就死扣到底结论是方向错了。像日本氢能源,日本光刻机死扣激光源

用户10xxx63

最可怕的是 2nm几乎是芯片的极限了,别人到赛道尽头了,我们还有机会追赶,一旦追上,中国会把芯片打成白菜价,

欢乐谷 回复 07-20 17:41

你看看内存芯片,价格一直在涨,再创新高!

无聊 回复 07-20 14:36

如果是国家做芯片,我觉得还真能把芯片打成白菜价。企业就算了,人家不是做慈善的,号称纯国产的华为旗舰手机比含关税的苹果还贵,绝对会有人说国产的凭什么不能卖贵的,呵呵,是啊,工艺比别人差,别人还有关税,都能比别人卖的贵,关键还不是纯国产的号称纯国产,所谓的爱国韭菜真香。

VCc

🐖

雨夜流星

车到山前必有路,在复兴路上的中国面前就没有过不去的坎。

用户10xxx05

什么170亿?140亿?面积呢?什么乱七八糟的

信仰圣光吧 回复 07-20 13:36

应该是一个芯片内的晶体管数量

椿花湫月 回复 信仰圣光吧 07-25 07:33

但芯片也有大小的呀

A8898

极紫外线就是最短的光波线了,更短的目前没有找出来,都是各种忽悠纳米,和酒一样,忽悠年份[笑着哭][笑着哭][笑着哭]

如来神掌 回复 07-20 13:01

x射线

盐识平

intel早知道台积电和三星的制程有水分了,所以改叫intel7和4,对应的10纳米和7纳米。

奶茶杯定制 回复 07-23 23:43

以前听过一个网友这样评论过 三星的7纳米是达到百分之1就能叫7纳米 台积电是百分之30 英特尔是百分之70[裂开]

记忆

以后别说几纳米了,就说每平方米多少晶体管,这样最科学

认蒸你就熟了 回复 07-20 02:51

一平方米2纳米的晶体管就多咯[得瑟]

大牛比较懒 回复 07-23 10:54

目前中国自己能产的芯片每立方米10个晶体管,这样说您还满意吗?

小小

能做到以前的7nn就牛比了,目前用国产的设备肯定达不到以前7nm的水平,不管你们怎么吹都好,华为60发热就是芯片问题。

小心心

美国这样做 目的是为了激发中国的创造力 你看现在中国做得挺不错

流浪的可乐

只说晶体管数量,不说面积体积等于没说。

姬无忧 回复 07-21 18:51

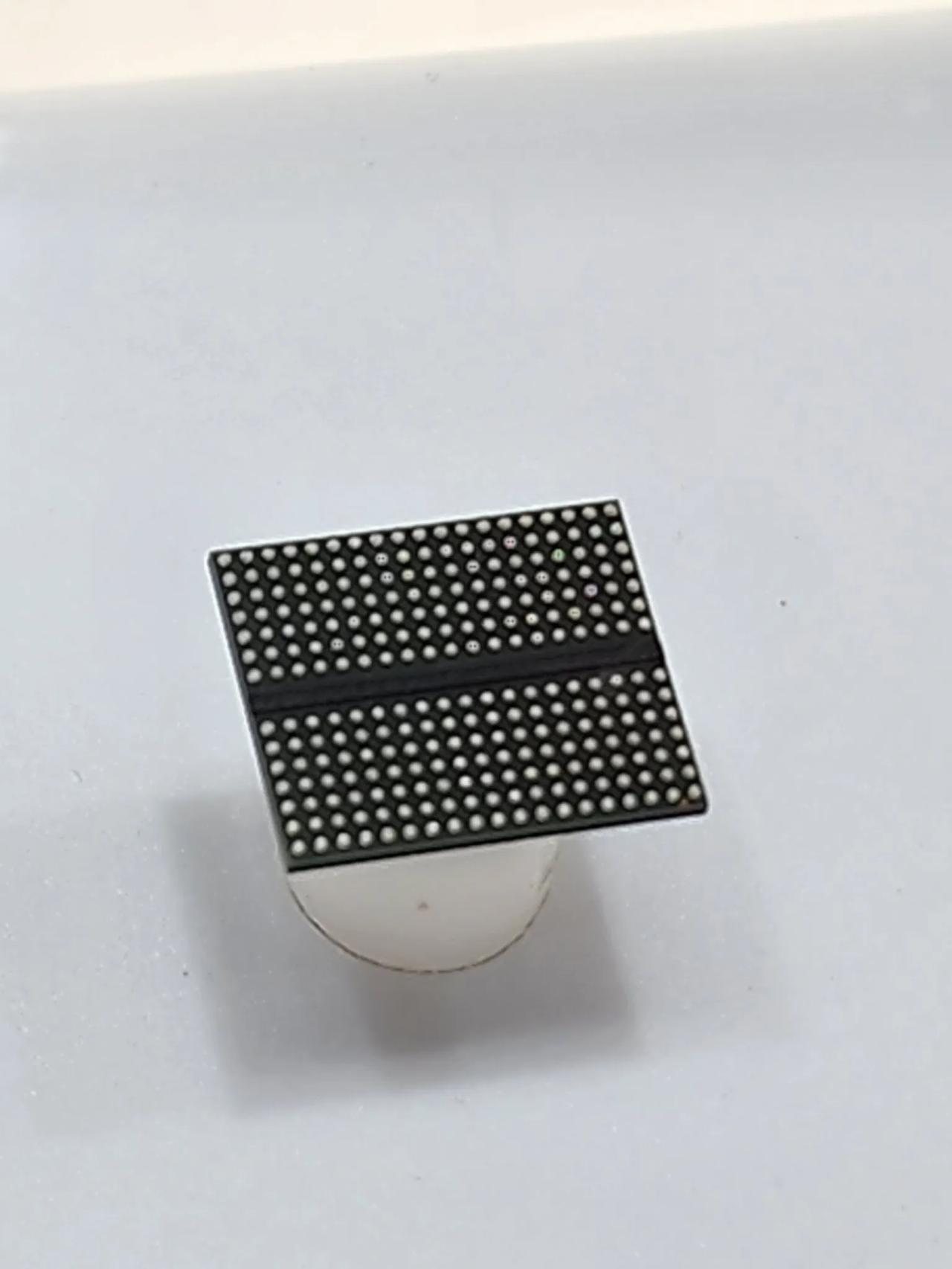

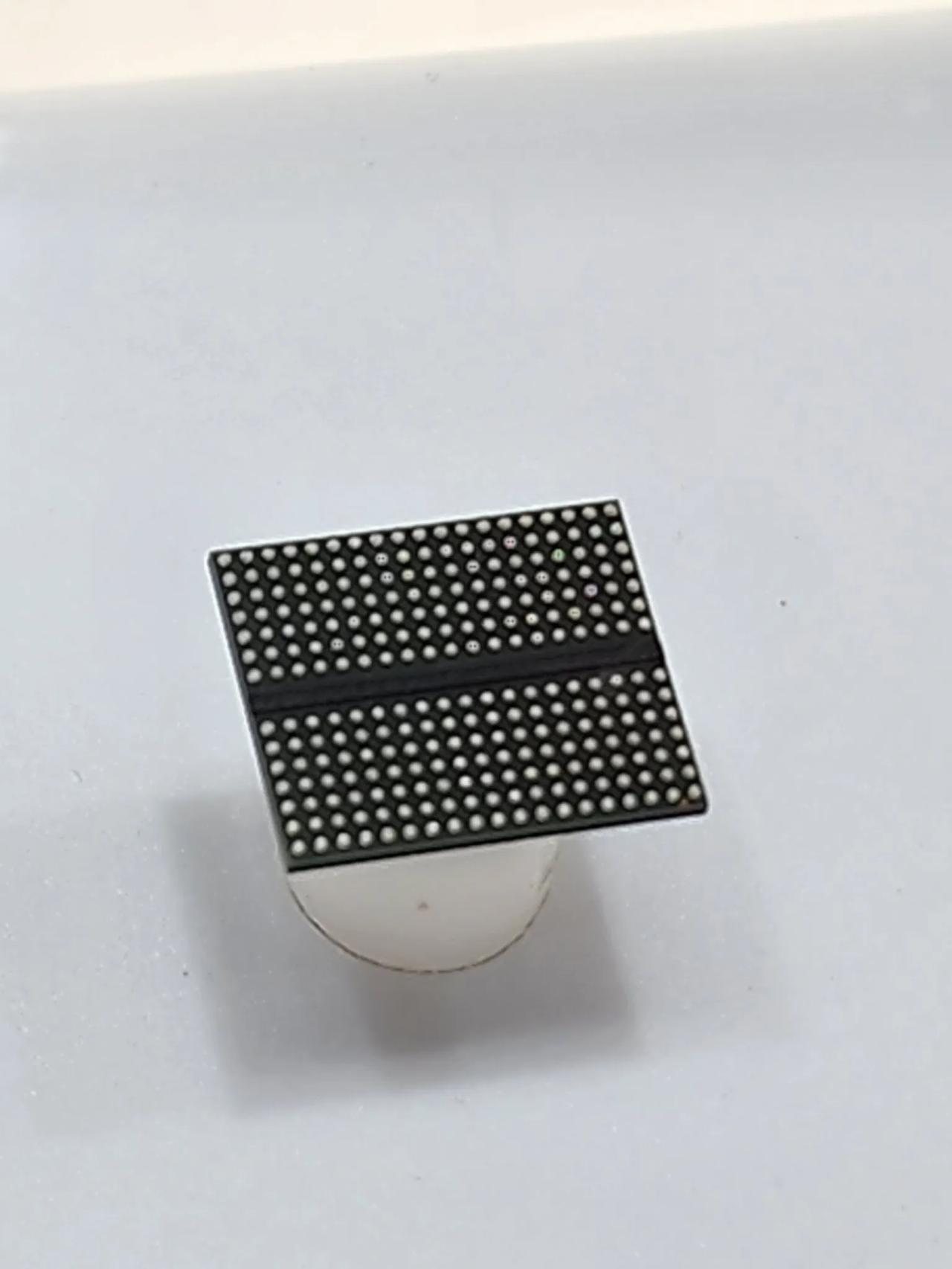

晶体管密度可以用堆叠层数的方式提升,存储芯片由于功耗和发热低,目前的工业可以在一块芯片上堆叠最多256层,目前CPU由于功耗大发热大最多只能堆叠2层,全球也只有AMD的7代锐龙CPU和英特尔14代CPU采用了这个工艺,麒麟9010可能是国产14纳米2层堆叠的芯片,晶体管密度快要接近台积电5nm工业,但是实际性能要差一点,发热也更大一点。

如来神掌

就小编这点肤浅的凡尔赛,能骗得了我泱泱大中华的流量?

cegndn

到底是你说的对,还是AI说的对?

木晨

反正就是遥遥领先

10088

吹牛逼

用户74xxx62

说IC的晶体管数量,业内默认是指每平方厘米。

姬无忧 回复 07-21 18:59

以前晶体管密度和工业制程成正比,现在不一定,AMD搞出来了2层堆叠的第7代锐龙CPU,在工业制程不变的情况下把晶体管密度提升了30%,性能提升了20%。还有堆叠层数达到256层的19nm工业的存储芯片如果计算晶体管密度的话相当于1nm以下了。

HeaVen

早你吹逼的时候咋没说是数字游戏了?现在这一套一套的在这诋毁别人,一副正义感的面孔

莲花亭主

美国人有时挺有意思的,本来国内高校争拨款八仙过海的,他搞了个制裁榜,类似广东工业大学这种名气大不的高校,恨不得制作个"挤进制裁榜,展现硬实行"的巨额横幅挂出来嘚瑟。

用户83xxx20

芯片大小你不算吗?芯片可以做大一点放更多的晶体管,但是这样耗电量就更大了。

赛赛

手机7纳米就完全够用了,我现在用的手机四年了一点毛病没有,感觉还能再用两年。

逍遥

麒麟9000还第一个用5纳米工艺呢,应该考虑的是性能比麒麟9000提升多少,放多少晶管那些都是宣传语!按芯片旧的制程标准,现在的2纳米也只是28纳米的标准