本文将介绍CMOS反相器电路中的动态和静态功耗。

CMOS反相器的发展为集成电路提供了必要的功能,是技术史上的一个转折点。该逻辑电路突出了 CMOS 独特的电气特性,非常适合高密度、高性能数字系统。

CMOS 的优势之一是其效率。CMOS 逻辑仅在改变状态时才需要电流——仅维持逻辑高或逻辑低电压的 CMOS 电路消耗的功率非常小。一般来说,低功耗是一个理想的特性,当您试图将尽可能多的晶体管功能封装到一个小空间中时,它特别有用。

正如计算机 CPU 风扇提醒我们的那样,从集成电路中充分去除热量可能很困难。如果没有CMOS反相器和其他类似的CMOS电路,这将更加困难。本文将回顾 CMOS反相器的主要特性,并讨论其两种主要的功耗类型:动态和静态。

CMOS反相器的结构和工作原理CMOS反相器由NMOS晶体管和PMOS晶体管连接在一起组成。图1显示了基本CMOS反相器的原理图。

CMOS反相器的基本操作非常简单:

当输入端被驱动至逻辑高电压时,上部PMOS晶体管阻断电流,下部NMOS晶体管导通电流。因此,输出端子通过低电阻路径连接到0 V。

当输入端被驱动至逻辑低电压时,PMOS导通,NMOS阻断。输出通过低电阻路径连接到VDD型.

这样,逻辑高电平输入产生逻辑低电平输出,逻辑低电平输入产生逻辑高电平输出。

动态功耗每当电流流过导电元件时,就会消耗功率。我们在功率的基本公式中看到了这种关系:P = I x V 虽然CMOS反相器在稳态下不需要电流,但在其逻辑转换过程中会消耗功率。这种动态功率损耗有两种类型:

开关功耗。

短路功耗。

开关功耗当输入逻辑转换发生时,瞬态电流必须流动,以便对电路中的电容进行充电或放电。在低输出到高输出转换期间,电流流动以对负载电容进行充电,因为输出电压增加到VDD型.图 2 显示了该电流所采用的路径。

图2.从低输出到高输出转换期间的充电电流。

图2.从低输出到高输出转换期间的充电电流。电流也会在高低输出转换期间流动(图 3),当输出电压降至地电位时,电容会放电。

图3.从高到低输出转换期间的放电电流。

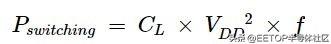

图3.从高到低输出转换期间的放电电流。为了估算CMOS反相器的开关损耗,我们使用以下公式:

公式中:

CL 是预期的负载电容f 是开关频率。CL × VDD2计算一个开关周期所需的能量。为了将这个结果从能量转换为功率,我们将其乘以每秒循环次数 (f),得到上面的等式。

短路功耗另一种动态功耗是由短路电流引起的。也称为击穿电流,这是反相器逻辑电平转换期间发生的瞬态情况。

当 CMOS 反相器处于逻辑状态时,其两个晶体管之一处于非导通模式。因此,电流不容易从V DD流向地。然而,当反相器改变状态时,会出现一个短暂的交叉周期,在此期间,NMOS 和 PMOS 都具有一定程度的导电性。当电流流过由此产生的短路时,能量就会损失(图 4)。

图 4. NMOS 和 PMOS 晶体管在逻辑电平转换期间短暂产生短路,会使电流从VDD流向地。静态功耗

图 4. NMOS 和 PMOS 晶体管在逻辑电平转换期间短暂产生短路,会使电流从VDD流向地。静态功耗在整篇文章中,我们都避免说“CMOS 反相器中绝对不会出现稳态功耗”之类的话。事实上,场效应晶体管并不是理想的开关。即使在关断状态下,漏电流也可以从漏极流向源极以及从漏极或源极流向衬底。

如果这些漏电流的大小已知,则可以使用以下公式计算产生的功耗:

过去,动态功耗远高于静态功耗。如今,静态功耗可能很大。随着CMOS特征尺寸的减小,其对总功耗的贡献接近动态功耗。

最后,请注意,静态功耗是工作温度的函数。随着温度的升高,静态功耗也会增加。

结束语CMOS反相器既可以作为独立的逻辑运算,也可以作为高阶逻辑运算的组件。CMOS 反相器还用于在驱动能力较低的数字电路的输出端创建缓冲器。反相器提供模拟放大以减少信号的上升和下降时间。它们还可以将信号恢复到完整的逻辑电平。

来源:EETOP编译自allaboutcircuits