在本节中,我们将研究使用内存和逻辑的完整3D 垂直堆栈的 PIM 架构。

我们在第 2 节中描述的 HBM-PIM。

4.4 是 2.5-d 解;它通过硅中介层将逻辑模块和 HBM 并排放置。另一方面,全 3 维堆叠意味着底部的逻辑芯片与顶部的 HBM 等堆叠存储器的集成。由于它堆叠了主计算芯片和堆叠内存芯片,因此它比 HBM 更先进,期望两个实体之间实现更节能的数据通信。混合存储立方体(HMC)就是主要的例子。然而,由于 3-d 堆叠芯片之间严格的物理和时序限制,3-d PIM 的实现可能很困难。所有提出的 3-d PIM 架构均仅使用仿真进行评估。在本节中,我们将简要回顾一些基于 3-d PIM 架构的工作。

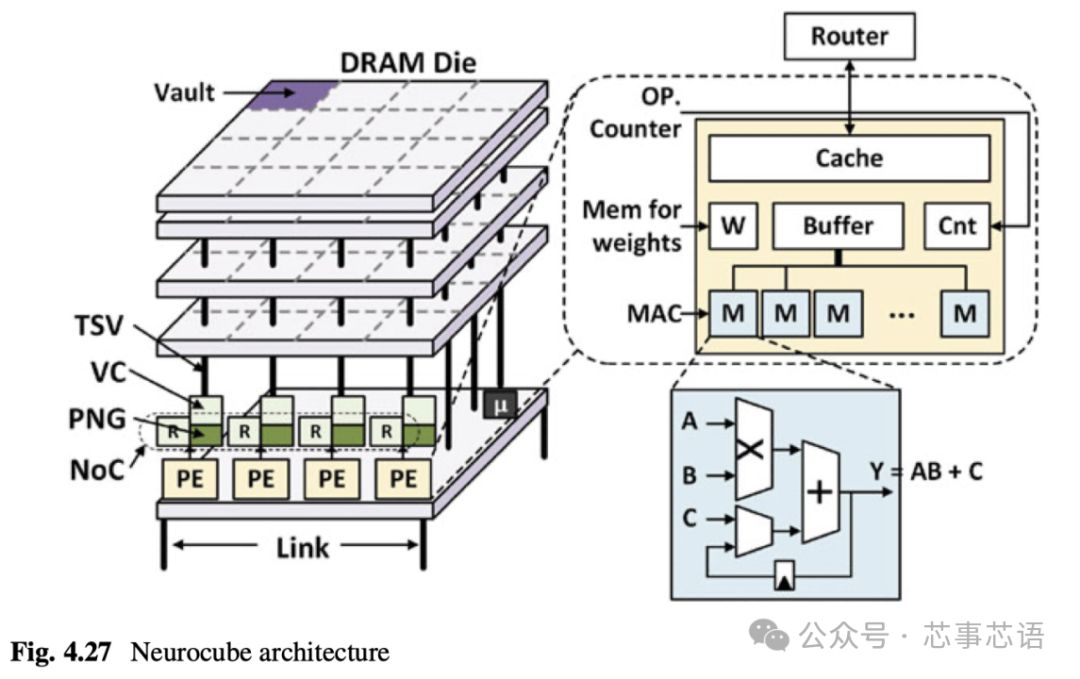

4.5.1 NeurocubeNeurocube [5]是最早的架构之一,它展示了将 3-d 高密度内存包用于深度神经网络的可行性和性能优势。如图 4.27 所示,Neurocube 架构设计在 HMC 的逻辑芯片中,由全局控制器、可编程神经序列生成器(PNG)和通过片上网络连接的处理元件(PE)组成。同时,每个 PE 被分配给一组垂直连接的 DRAM 存储体,称为存储库。 PE 是主要计算单元,具有多个乘法累加 (MAC) 单元,可加速深度神经网络计算。 PNG 使用保管库控制器生成对保管库的正确数据访问序列,并将它们推送到 MAC 单元。具有二维网状拓扑的片上网络将所有 PE 互连,以实现各种数据映射和操作的库间通信。

俄罗斯方块[6]架构是基于Neurocube架构的。HMC 堆栈垂直分为 16 个 32 位宽的存储库,其中每个存储库充当控制内部所有存储体的通道(每个芯片两个存储体)。与Neurocube不同的是,Tetris选择了处理单元的阵列设计。每个处理单元都包含一个小型全局片上缓冲区,以最大限度地提高数据重用机会。俄罗斯方块还提出了一种高效数据流的调度算法。它专注于输入数据重用,通过平铺将输入特征映射缓冲在全局缓冲区上,并将输出特征映射和权重过滤器直接传输到外部存储器或从外部存储器传输。图 4.28 说明了俄罗斯方块架构。

iPIM [7]折衷了 Neurocube 和 Tetris 使用的 3-d PIM 方法以及 Newton 和 HBM-PIM 使用的银行级 PIM 方法,以增加有效计算带宽并减少数据移动所消耗的能量TSV。如图 4.29 所示,iPIM 的保管库架构将控制和执行的角色解耦。逻辑芯片包括执行复杂控制操作的 iPIM 核心,例如指令解码和发布以及存储体控制。另一方面,集成到存储库的每个 DRAM 芯片中的进程组 (PG) 在近存储区执行简单但内存密集型操作。为了实现大规模的bank级并发执行,iPIM提出了单指令多bank(SIMB)指令,包括计算、索引计算、库内/库间数据移动和同步操作。

-对此,您有什么看法见解?-

-欢迎在评论区留言探讨和分享。-