电气间隙与爬电距离

电源与保护地(PGND)间电气间隙≥2mm,爬电距离≥2mm(保险管前)或≥1.4mm(保险管后)。

PGND与其他信号(如GND、低速信号)间距≥2mm,接口隔离区间距≥100mil。

高压区域(-48V系统):

通用连接器:需按电压等级验证针脚间距;专用电源连接器(如ATCA Zone1)可豁免。

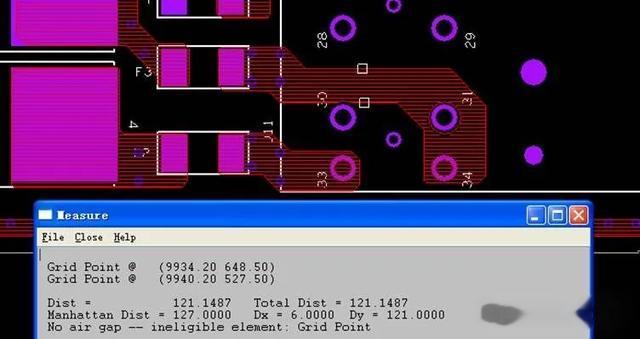

检查方法:通过PCB工具高亮网络,手动测量关键区域间距。

通流能力

连接器选型需满足最大负载电流(含异常短路电流),确保PCB铜箔先于连接器烧毁。

通用连接器需优化电源/地针脚分布,减少电流路径阻抗。

二极管/电感/磁珠:前后走线宽度一致,避免突变;RC滤波电阻两侧线宽匹配。

如下图中,磁珠隔离后,给器件的4个电源管脚供电,走线太细,宽度只有5mil;

铺铜通流能力

按公式或工具计算线宽(经验值:1Oz厚度PCB,40mil过1.5A),需覆盖正常及异常电流(以保险管熔断电流为基准)。

例子:

对于-48V电源,我们首要关注的是铺铜过流能力(-48V在使用之前通常要做缓起和滤波,所以不会布电源层)和爬电距离。铺铜应该考虑过流能力是否足够,这个不仅仅要考虑正常情况下的过流能力,而且要考虑异常情况下的过流能力,就是如果单板短路了,是否能保证PCB不会首先被烧掉。如果器件被烧了,更换器件就OK了,但如果PCB被烧了,整板就报废了,所以首先要保证PCB不会被烧掉。那铺铜的过流能力要满足多大的电流呢?这和具体应用有关,有一个诀窍,就是以-48V的保险管电流为标准,只要保证铺铜的过流能力大于保险管的最大电流,就能保证PCB不会被烧掉。经验数据是每40mil可以过1.5A电流。-48V电源铺铜的通流能力需要沿着供电路径一直审查下去,直到-48V进入电源平面为止。

例如下图中,两路-48V从连接器经过铺铜到两个保险管,保险管的最大电流是5A,铺铜的宽度是120mil左右,这样的话铺铜的通流能力只有4.5A,要小于保险管熔断的5A,这样就有可能PCB先烧了。

高压区(如-48V):优先采用实心铺铜,避免细长瓶颈;路径全程通流需≥保险管容量。

平面层设计

电源层内缩:电源平面相对地平面内缩≥50mil,距板边≥20mil。

分割线宽度:常规区域≥30mil,安规区域≥80mil,BGA区域≥20mil。

三、过孔设计规范过孔通流能力

每个过孔按1-1.5A设计(10mil孔径),路径总过孔数≥最大电流/单孔通流。

重点关注二次电源模块(如12V→5V)及大电流区域(如FPGA供电)。

过孔布局

电源换层时过孔均匀分布,避免集中瓶颈;优先选用大尺寸过孔(如12mil/24mil)。

禁止高速信号过孔穿过电源敏感区(如MOS管下方)。

四、DC/DC设计规范布局与滤波

输入电容紧贴上管(MOSFET)放置,缩短高di/dt回路。

减小SW平面面积,减小dv/vt的铺铜面积

反馈与采样

电压反馈:大电流电源采用远端差分反馈,小电流用近端单端反馈;分压电阻靠近控制器。

电流采样:差分走线,远离干扰源;采样线从电感两端对称引出。

关键走线

驱动信号(GATE/BOOT):线宽≥15mil,路径最短化,避免换层缩颈。

信号隔离

高速信号(如PCIe、时钟)远离SW平面、原理高频电流环路≥100mil,避免平行走线。

地平面优化

芯片GND与电源滤波电容GND隔离,避免共地噪声耦合(如LDO地独立铺铜)。

敏感电路(如PLL)采用局部地平面,并通过磁珠/电感隔离。

噪声抑制

大电流DCDC输入串接电感(如1μH)并并联滤波电容(如470μF),抑制开关噪声耦合。

散热铜皮亮铜处理,高热器件远离敏感区域。

六、散热与可靠性设计热设计

高功耗器件(如MOS管、电源芯片)下方大面积铺铜并添加散热过孔。

载流瓶颈检查

重点审查BGA、过孔密集区、狭窄通道的电源/地有效宽度。

仿真验证大电流路径压降(如FPGA Core电源)。

七、安规与工艺要求高压区处理

-48V与其他低压电源间距≥2mm,开窗区域增加丝印警示。

保险管前后分区明确,避免跨区交叉布线。

DFM要求

电源模块输入/输出布线无交叉,减少回流路径干扰。

关键信号线避免直角走线,优先采用45°或圆弧转角。

【在线培训】硬件工程师(单板电源设计)中级