TSV,全名Through-Silicon Via,又叫硅通孔工艺。

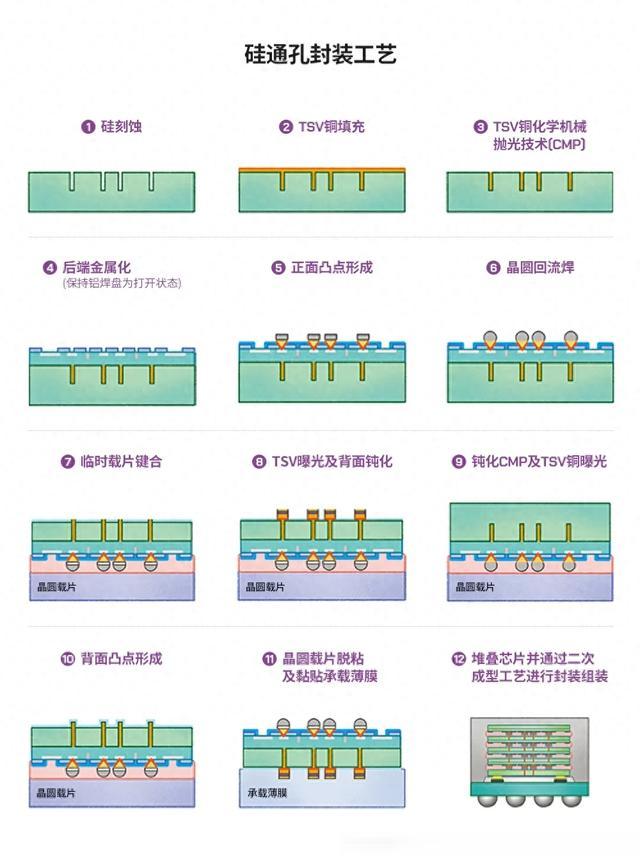

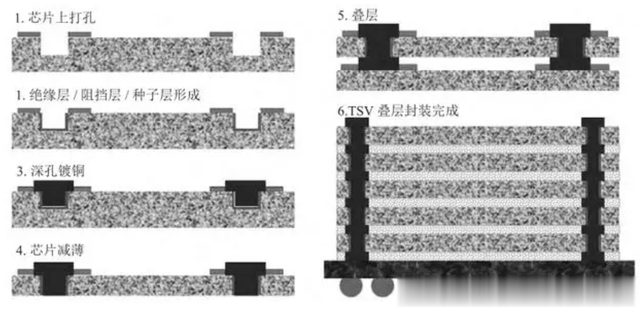

TSV硅通孔工艺的流程,主要有以下步骤:

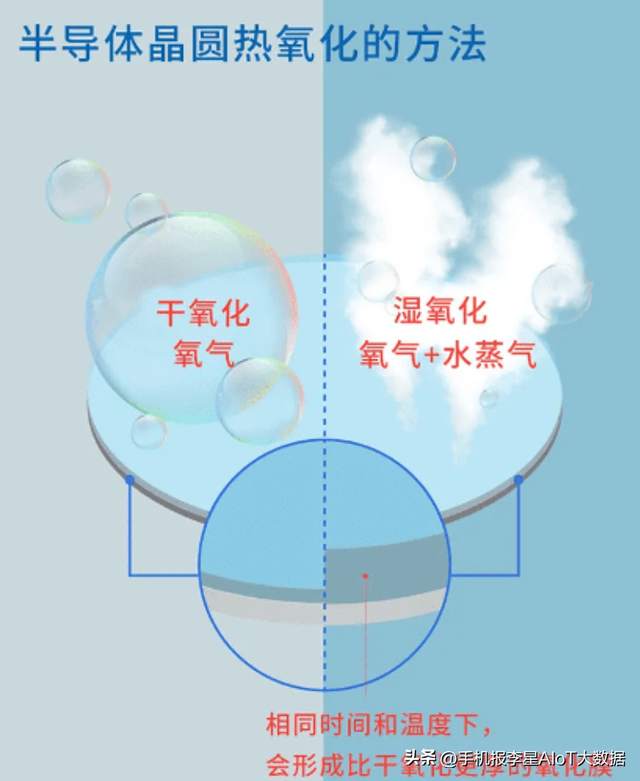

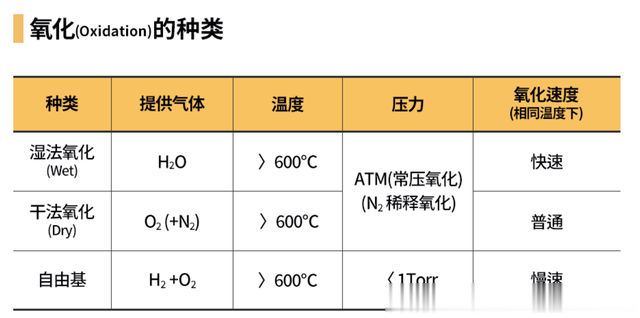

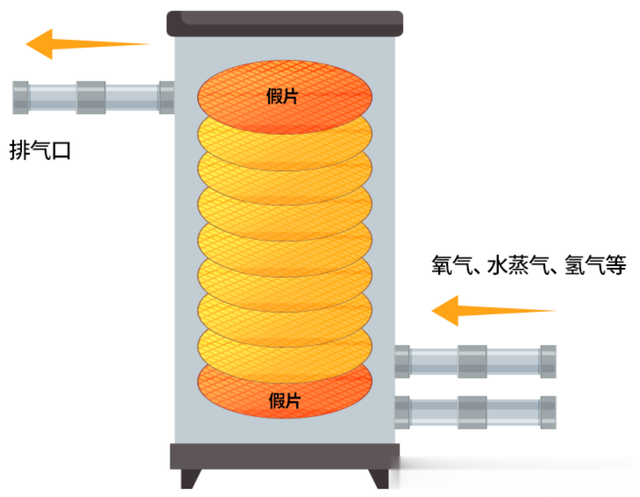

1、硅基底准备:先在硅晶圆上制作二氧化硅(SiO₂)层,这层SiO₂可以通过热氧化或等离子体增强化学气相沉积(PECVD)方法形成。质量最高,厚度控制最精确,均匀性最好的是炉管氧化方法,就是在通氧气的炉管中,通过高温,让氧气和硅发生化学反应,生成SiO2。这样就在Si的表面生成了薄薄的一层SiO2。

硅片的热氧化 是一种在硅片表面上生长二氧化硅薄膜的手段。热氧化制备SiO2工艺就是在高温、氧化物质(氧气或水汽)存在条 量好,具有较高的化学稳定性及工艺重复性,且物理性质和化学性质受工艺条件波动影响小。热氧化工艺制备二氧 化层方法。 硅表面总是覆盖着一层二氧化硅膜,即使刚刚解理的硅也是如此。在空气中一旦暴露,立即就生长出几个原子层的 定性和电绝缘性。二氧化硅薄膜具有与硅的良好亲和性,稳定的物理化学性质、良好的可加工性,以及对掺杂杂质 二氧化硅薄膜的作用 1. 作为绝缘层,阻止电路之间的漏电 2. 作为保护层,防止后续的离子注入和刻蚀过程中对硅晶圆造成损伤 3. 作为掩膜层,定义电路图案。

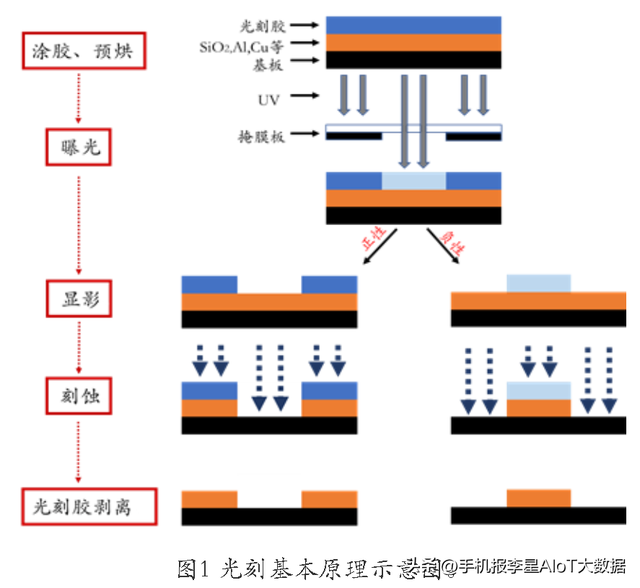

2、光刻:把光刻胶(Photoresist)涂布在晶圆的SiO₂层上,进行烘培。

光刻胶供应商会提供软烘培温度和时间的范围,之后光刻工艺师再把这些参数优化。负胶必须要在氮气中进行烘培,而正胶可以在空气中烘培。软烘培的方法很多,他们是通过设备和三种热传递方法组合来完成的。

热传导的三种方式是:传导、对流和辐射。传导是热量通过直接接触物体的热表面传递的。热板就是通过传导加热。在传导过程中,热表面的振动原子使待加热对象的原子也振动起来。由于它们的振动和碰撞,这些原子就会变热。

3、图案化:图形化工艺包括曝光(Exposure)、显影(Develope)、刻蚀(Etching)和离子注入等流程。其中,刻蚀工艺是光刻(Photo)工艺的下一步,用于去除光刻胶(Photo Resist,PR)未覆盖的底部区域,仅留下所需的图案。这一工艺流程旨在将掩模(Mask)图案固定到涂有光刻胶的晶圆上(曝光→显影)并将光刻胶图案转印回光刻胶下方膜层。

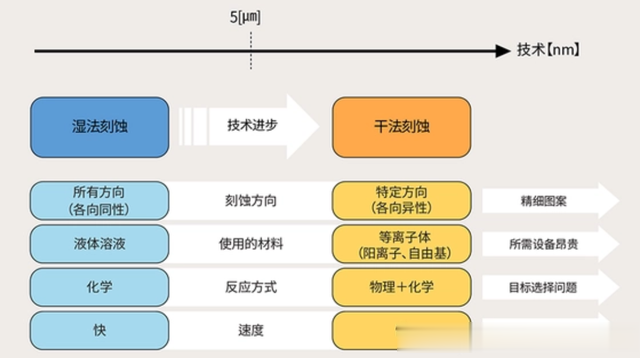

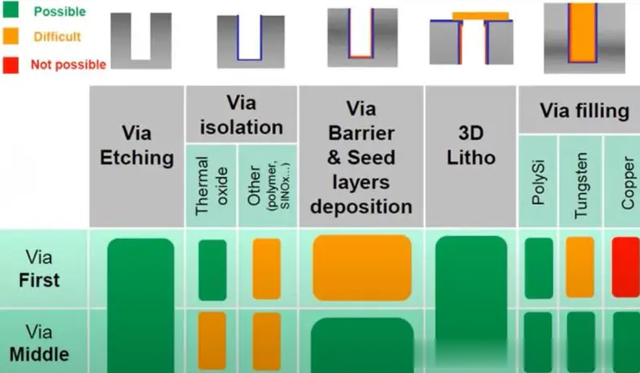

4、硅蚀刻:使用光刻图案作为掩模,采用DRIE在硅基底中蚀刻出通孔。随着电路的关键尺寸(Critical Dimension, CD)小型化(2D视角),刻蚀工艺从湿法刻蚀转为干法刻蚀,因此所需的设备和工艺更加复杂。由于积极采用3D单元堆叠方法,刻蚀工艺的核心性能指数出现波动,从而刻蚀工艺与光刻工艺成为半导体制造的重要工艺流程之一。

刻蚀是半导体制造工艺、微电子IC制造工艺以及微纳制造工艺中的一种相当重要的步骤。刻蚀是用化学或物理方法有选择地从硅片表面去除不需要的材料的过程,它是通过溶液、反应离子或其它机械方式来剥离、去除材料的一种统称。苏州博研掌握离子束刻蚀(IBE)、深硅刻蚀(DRIE)、反应离子刻蚀(RIE)、聚焦离子束刻蚀(FIB)、电感耦合(ICP)等离子刻蚀等多种刻蚀方式。

在2D(平面结构)半导体小型化和3D(空间结构)半导体堆叠技术的发展过程中,刻蚀工艺也在不断发展变化。在20世纪70年代,2D半导体为主流,电路关键尺寸(CD)从100微米(㎛)迅速下降到10微米(㎛),甚至更低。在此期间,半导体制造流程中的大部分重点工艺技术已经成熟,同时刻蚀技术已经从湿法刻蚀过渡到干法刻蚀。对于层切割技术,最先采用的是化学湿法,这是一种相对简单的技术。由于从20世纪70年代早期开始,化学湿法难以满足5微米(㎛)关键尺寸的要求,从而开发出利用等离子体的干法。发展到今天,刻蚀工艺大多采用干法,而湿法刻蚀技术后来发展应用于清洁过程。

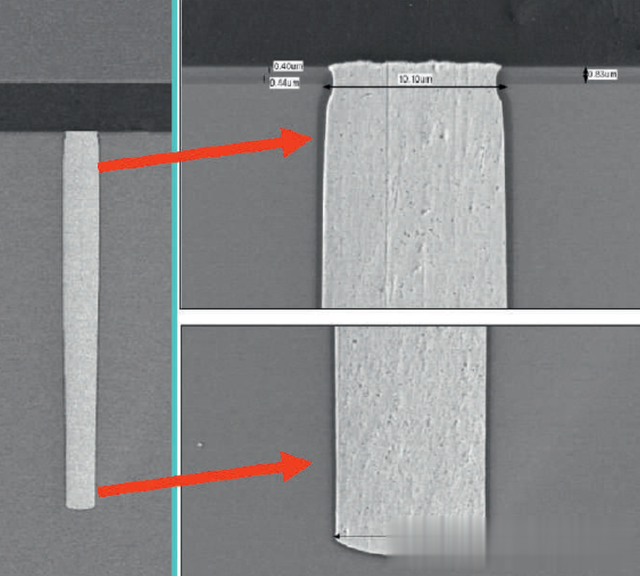

其中TSV的孔成型,很多也是采用蚀刻方案。孔成型的方式有激光打孔、干法刻蚀、湿法刻蚀等。基于深硅刻蚀(Deep Reactive Ion Etching,DRIE)的 Bosch工艺是目前应用最广泛工艺。反应离子刻蚀(Reactive Ion Etching,RIE)工艺是采用物理轰击和化学反应双重作用的刻蚀,Bosch 工艺通过刻蚀和保护交替进行来提高 TSV 的各向异性,保证 TSV 通孔垂直度。

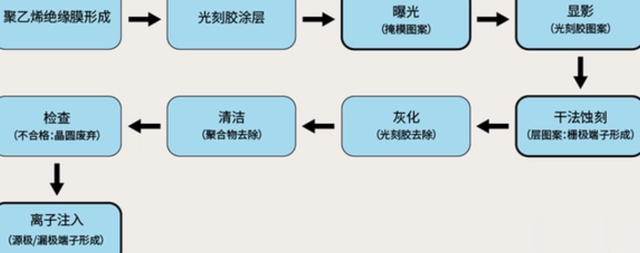

刻蚀工艺流程始于形成薄膜,在其上施加光刻胶,并进行曝光、显影、刻蚀、灰化、清洁、检查和离子注入等步骤,以形成三个Tr端子,这是半导体制造的核心工艺。如果在显影过程中不能顺利切割光刻胶,则剩余的光刻胶会妨碍刻蚀。如果在刻蚀过程中未能对目标层进行充分刻蚀,则不能按计划注入离子,因为杂质会妨碍离子注入。如果干法刻蚀后未能彻底清除残留的聚合物,也会产生同样的后果。如果由于时间控制失败,等离子体的离子气体量太大或薄膜刻蚀过度,会对下层薄膜造成物理性损伤。

因此,在干刻蚀工艺中精准控制终点(EOP:End of Point)至关重要。彻底检查刻蚀条件以及灰化和清洁过程也非常重要。

5、去除光刻胶:在蚀刻完成后,去除光刻胶以准备接下来的层沉积步骤。

6、沉积绝缘层和阻挡层:通过PVD,PECVD或原子层沉积(ALD)技术在孔壁上沉积一层二氧化硅来作为绝缘层,防止电子窜扰;然后沉积一层导电的阻挡层,如钛/铜(Ti/Cu)或钽/铜(Ta/Cu),以便后续的铜镀层能更好地附着,且能防止电子迁移。

其中镀膜是一种常用的表面处理工艺,一般是在真空环境下,将某种金属或非金属以气相的形式沉积到材料表面,形成一层致密的薄膜,镀膜质量对半导体器件的功能形成至关重要。

TSV 孔内绝缘层用于实现硅村底与孔内传输通道的绝缘,防止 TSV通孔之间漏电和串扰。TSV 孔壁绝缘介质材料选用无机介质材料,包括PECVD、SACVD、ALD 和热氧化法。

沉积阻挡层/种子层:在2.5D TSV 中介层工艺中,一般使用铜作为 TSV 通孔内部金属互联材料。在电镀铜填充 TSV 通孔前,需在 TSV 孔内制备电镀阻挡/种子层,一般选用 Ti、Ta、TiN、TaN 等材料。TSV 电镀种子层起着与电镀电极电连接并实现 TSV 孔填充的作用。

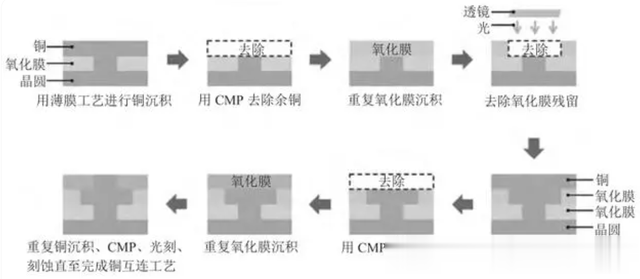

7、铜电镀:在绝缘层和阻挡层上进行铜镀层,以填充TSV孔洞。一般通过电镀方式完成。电镀完成后,进行退火工序,释放应力。TSV 深孔的电镀填充技术是 3D 集成的关键技术,直接关系到后续器件的电学性能和可靠性。可以填充的材料包括铜、钨、多晶硅等。

电镀液成分主要包括硫酸、铜离子、氯离子、加速剂、抑制剂和整平剂等六种组分。理想的填充过程是自底向上的沉积过程,这就需要镀铜溶液中抑制剂、加速剂等不同添加剂的合理配比,达到“沟槽内加速、沟槽口抑制”的效果,从而实现低电阻率、无空洞和高可靠性的铜布线结构。

8、CMP(化学机械抛光)工艺和背面露头工艺:CMP 技术用于去除硅表面的二氧化硅介质层、阻挡层和种子层。TSV 背面露头技术也是 2.5DTSV 转接基板的关键工艺,包括晶圆减薄、干/湿法刻蚀工艺。传统的晶圆减薄技术包括机械磨削、CMP 和湿法腐蚀等。目前业界主流的解决方案是将晶圆的磨削、抛光、保护膜去除和划片膜粘贴等工序集合在一台设备内。

至此,一个完整的TSV工艺流程基本上走完了。

TSV 按照集成类型的不同分为 2.5D TSV 和3D TSV,2.5D TSV 指的是硅转接板上的 TSV,3DTSV 是指芯片上制作硅通孔,连接上下层芯片。

TSV 是 3D 系统集成的关键技术和发展趋势,目前已经可以实现深宽比为 10∶1 的 TSV 结构,且向着更高深宽比发展。随着工艺的提升,硅通孔的孔径越来越小,密度越来越大,目前最先进的TSV 工艺,可以在 1 mm 2 的芯片上制作高达 10 万个以上硅通孔,从而支撑更高密度的芯片互连,同样对 TSV 的电镀填充也提出了更高的工艺要求。