作为一名关注半导体行业的创作者,我最近频繁听到一种说法:浸润式DUV光刻机或许能突破技术瓶颈,制造出2nm芯片。这让我既兴奋又困惑——毕竟,在EUV光刻机被公认为先进制程“唯一解”的当下,这种可能性究竟有多大?

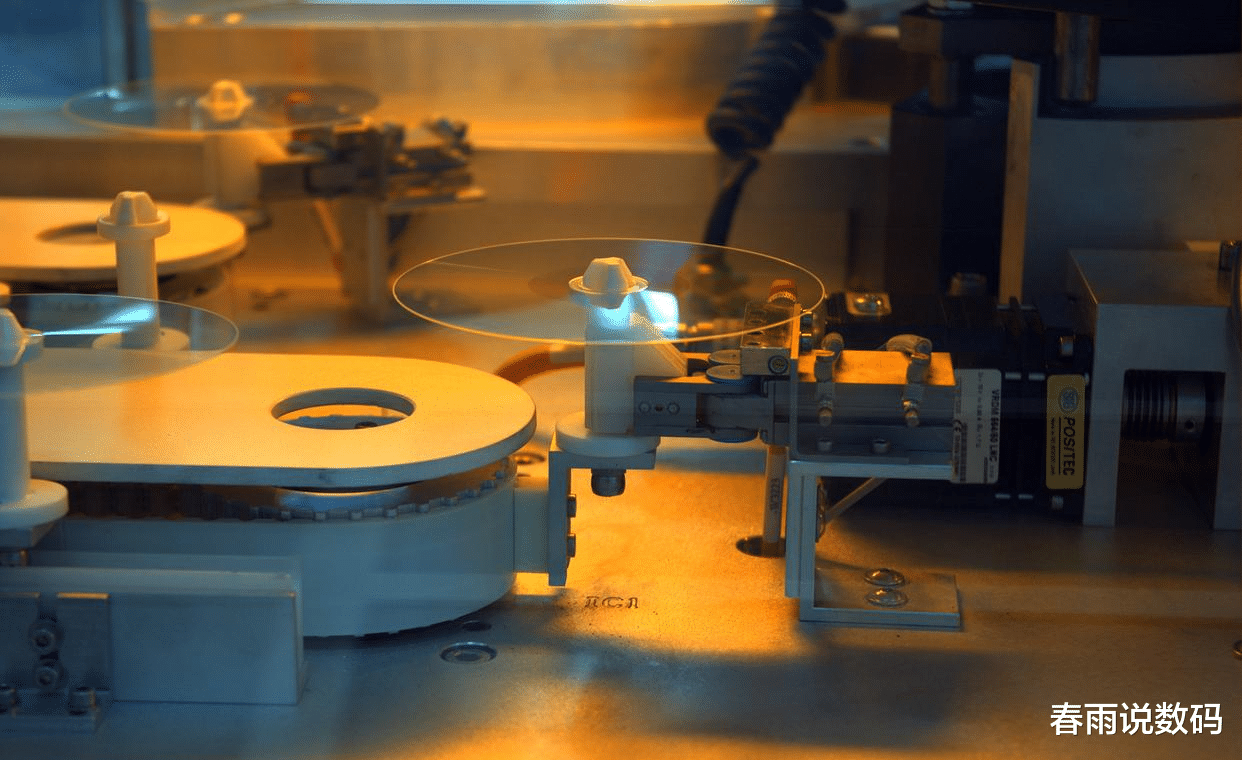

浸润式DUV光刻机(如ArFi机型)的核心原理并不复杂。它通过在水介质中折射193nm波长的光源,将等效波长缩短至134nm,从而提升分辨率。此前,这类设备已成功支持7nm工艺,但更进一步的制程需要依赖多重曝光技术。例如,通过SADP(双对准)和SATP(三对准)等工艺叠加,理论上可以将半间距缩小至10nm以下,这正是2nm制程的关键指标。

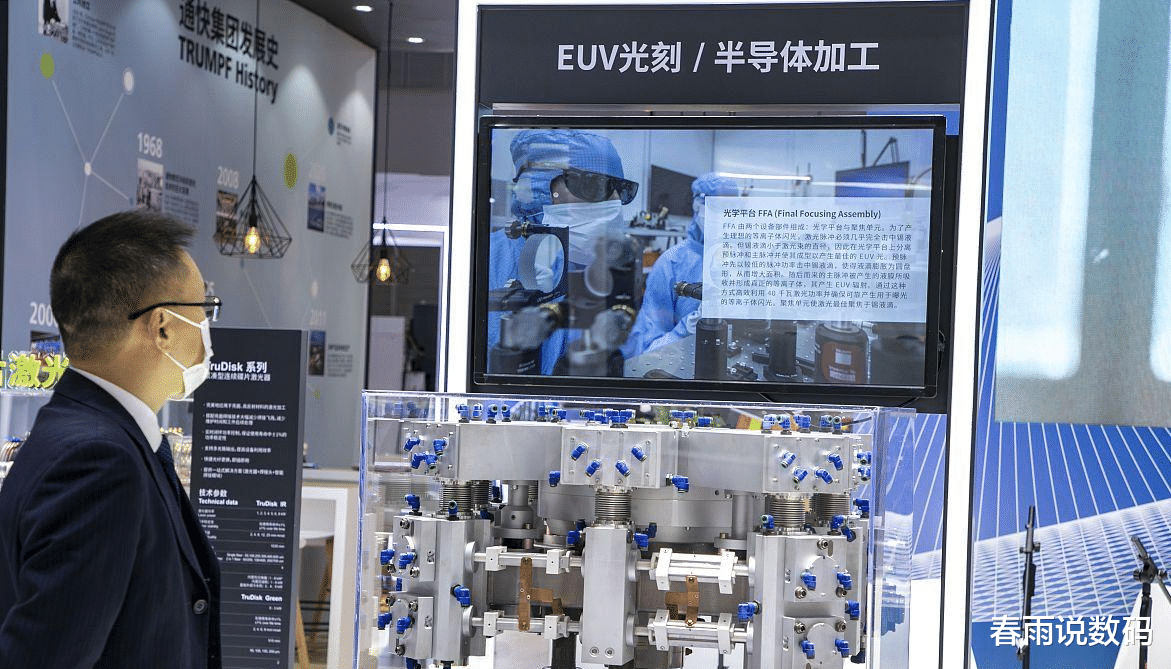

国际半导体技术路线图(2022年版)也指出,2025年2nm节点的最小半节距为10nm,而浸润式DUV通过多次曝光完全可能覆盖这一需求。换句话说,从物理极限来看,DUV并非“不能”,而是“如何实现”。

然而,理论可行不等于实际落地。我曾与业内工程师交流,他们提到一个关键问题:多重曝光的成本与良率。以台积电为例,其7nm工艺使用DUV时良率约为80%,但若用DUV强行推进到2nm,良率可能暴跌至50%甚至更低。这是因为每次曝光都会引入对准误差,叠加三次以上后,缺陷率呈指数级上升。

此外,经济账也算不过来。浸润式DUV单台成本约4-5千万人民币,而EUV高达上亿元7。但若为生产2nm芯片,DUV需要多次曝光,导致设备利用率下降、晶圆加工时间翻倍,整体成本反而可能超过EUV方案。一位同行调侃:“这就好比用三轮车跑长途——看似省钱,实际耗油更多。”

综合现有信息,我认为浸润式DUV制造2nm芯片的成功概率取决于三个维度:

技术突破

:能否开发更精准的对准算法?例如,ASML近期在套刻精度上的改进传闻,可能将误差控制在1nm以内。

市场需求

:如果2nm芯片仅用于小众高端领域(如军事、航天),低良率带来的高成本尚可接受。

产业链协同

:光刻胶、掩膜版等配套材料能否适配多重曝光工艺?目前日本厂商已推出专门针对DUV多次曝光的化学增强型光刻胶。

保守估计,短期(3-5年)内成功概率约30%。这并非否定DUV的潜力,而是因为EUV生态已趋于成熟——台积电、三星的2nm工厂均以EUV为核心7。但若地缘政治或供应链危机导致EUV断供,这一概率可能跃升至50%以上,正如中国部分企业正在探索的“替代路线”。

站在2025年的当下,浸润式DUV冲击2nm制程更像是一场“技术备胎”的突围。它或许无法取代EUV,但在特殊情境下,这种方案为行业提供了宝贵的灵活性。正如一位前辈所说:“芯片制造没有绝对的黑与白,在灰度的博弈中,多一条路就是多一分生机。”