IT之家2月19日消息,华硕电脑有限公司中国区总经理俞元麟的B站账户“普普通通Tony大叔”昨日分享了两位B站用户万扯淡、kurnal参与制作的AMD锐龙AIMax+395"StrixHalo"处理器芯片结构分析。

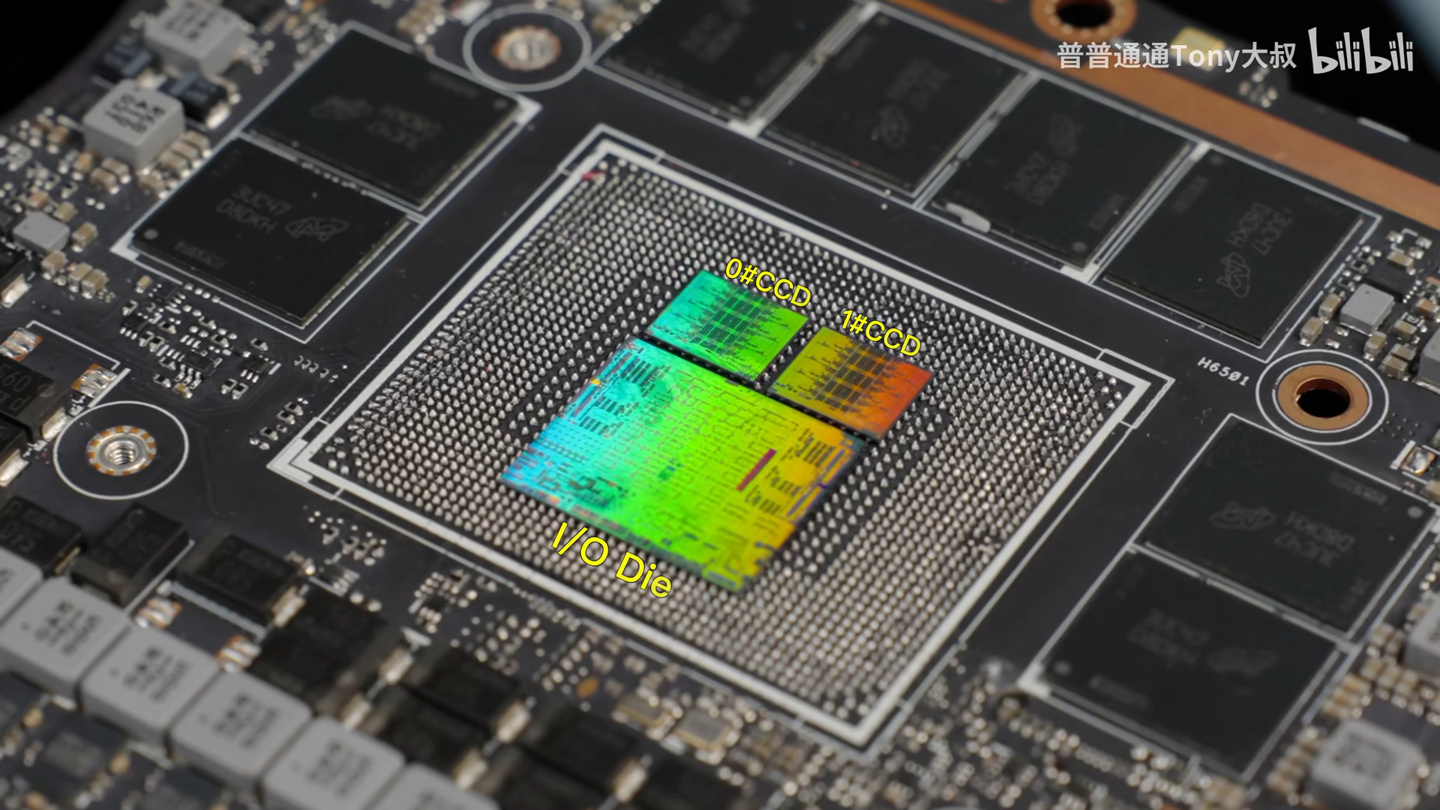

AMD在锐龙AIMax+395上采用了两颗4nm制程CCD芯片(每颗面积67.07mm2)和一颗同样也是台积电4nm的IOD芯片(面积307.584mm2),其中后者内含20WGP的超大规模核显。

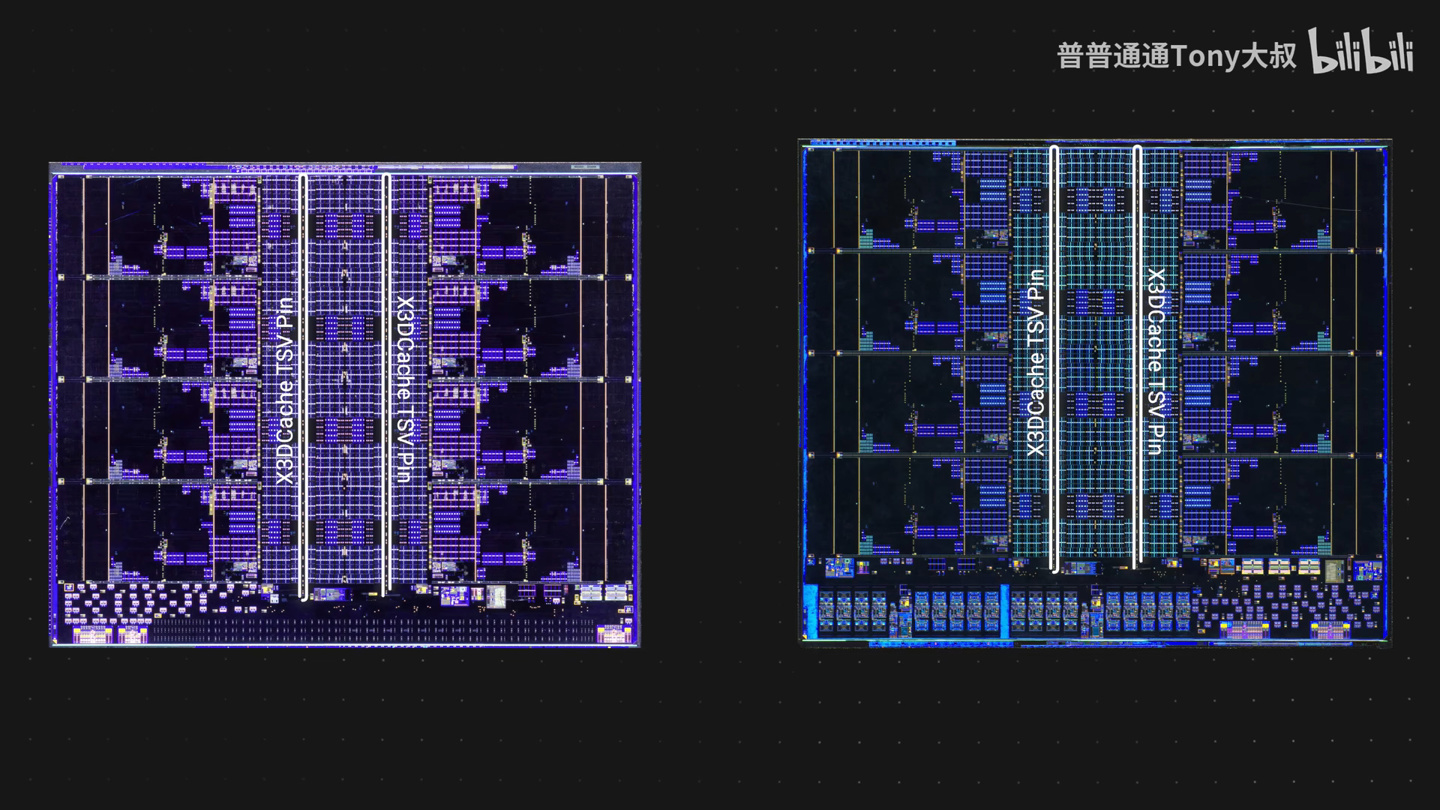

其中在CCD部分,AMD大体上复用了桌面端锐龙9000"GraniteRidge"处理器的CCD核心区域IP设计,因此"StrixHalo"芯片保留了用于3DV-Cache集成的TSV接口引脚。

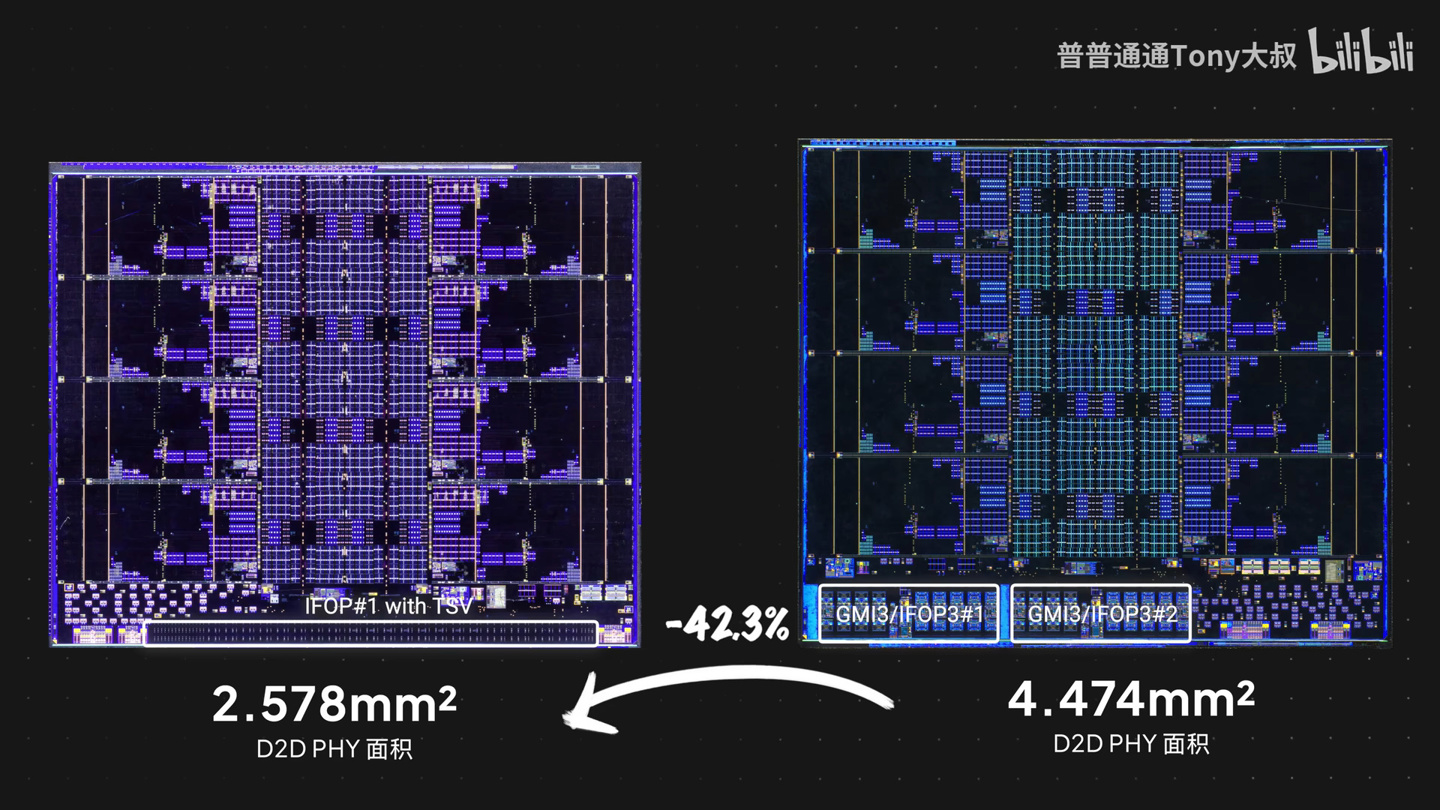

不过,AMD调整了CCD的边缘I/O,由基于SerDes的互联改为了水平扇出封装,这意味着"StrixHalo"所用CCD在纵向上缩短了0.34mm,互联区域面积缩小了42.3%。

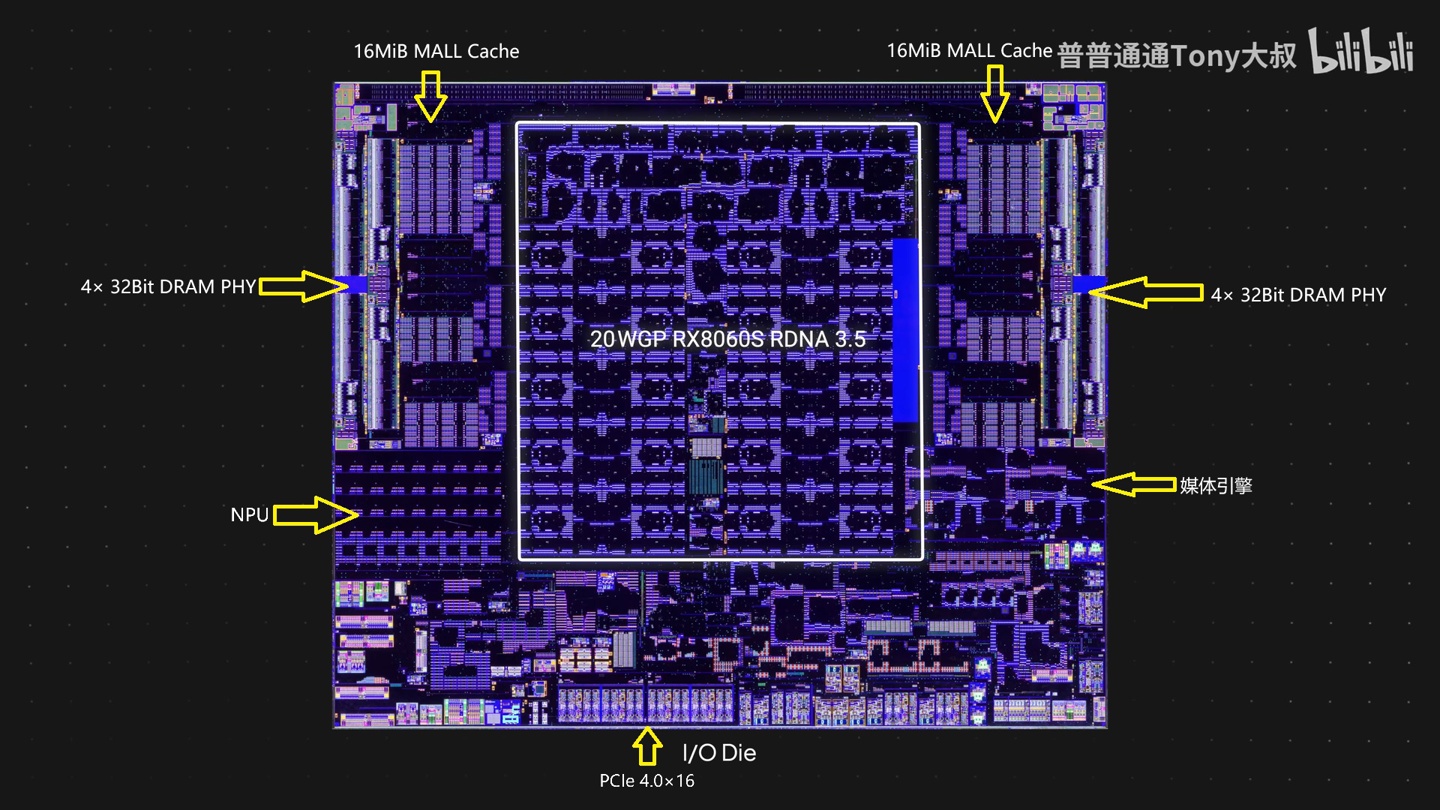

而在IOD部分,其中间区域自然是分为两簇的大型RDNA3.5核显,左右稍微靠外部分则是两片16MiB的MALLCache(IT之家注:即InfinityCache),来到边缘位置则是一共8组、合计256bit的DRAM内存接口。

"StrixHalo"IOD下方则分布了NPU、媒体引擎、PCIe接口在内的一系列其它电路。