多芯片 ESOP 封装集成电路产品分层问题研究

伍江涛

摘要:

ESOP 封装集成电路本身因为底部存在散热片,生产和使用过程中湿气容易从散热片边缘侵入集成电路内部,造成集成电路吸潮和回流焊时出现高温分层问题;多芯片集成电路集成了多个芯片、多种固晶胶水以及多次上芯的生产工艺过程,造成该类集成电路内部各材料间作用力复杂,容易出现结合力降低造成的分层问题。将上述两种结构相结合的多芯片 ESOP 封装集成电路就存在更大的分层风险。通过上芯工艺设计、材料间可靠性性能研究验证和生产过程控制,可以解决多芯片 ESOP 封装集成电路分层问题,实现了该类封装产品的大批量稳定性生产。

0 引言

集成电路分层问题一直是封装过程的重点控制项目,分层问题从封装材料、工艺、生产过程,一直持续到客户方的产品储存和回流焊应用等各个过程,成为集成电路失效的主要原因之一。

ESOP 类的散热片外置封装集成电路,外部散热片成为外部湿气的主要侵入通道,造成该类型封装产品较容易出现吸潮和回流焊后分层问题;ESOP类集成电路基岛部分与塑封料是单面粘合,粘合强度和密封性能弱于双面粘合的 SOP 封装,再加上多芯片集成电路集成了多个芯片、多种固晶胶水以及多次上芯的生产工艺过程,造成该类集成电路内部各材料间作用力复杂,容易出现结合力降低造成的分层问题。

考虑成本、外形尺寸、增强功能及提高功率等多方面需求,多芯片结构 ESOP 外形的封装集成电路产品的应用越来越广,对于该类产品的分层控制要求也越来越高。从减少湿气侵入通道和时间,增强各材料间作用力、提高集成电路抗分层能力以及生产过程控制等多个方面研究,需要总结出一套有效的分层控制流程,解决多芯片 ESOP 封装集成电路的分层控制问题。

1 产品设计

1.1 多芯片图纸设计

多芯片封装产品结构设计中,因为芯片数量较多,需要控制芯片到基岛边缘、芯片之间距离以及芯片角度等多方面影响。这类设计造成分层影响的因素如表 1 所示,需要在产品设计中考虑影响因素。

1.2 引线框架基岛结构设计

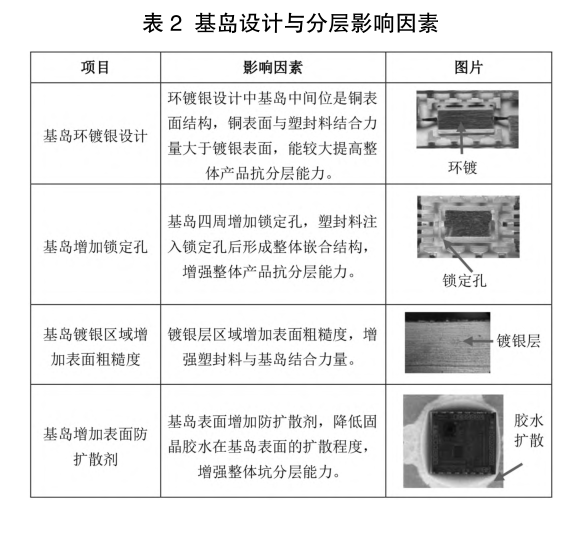

多芯片 ESOP 封装集成电路产品的引线框架承载了多颗集成电路芯片,其基岛设计明显大于普通的集成电路产品。这样的结构设计造成整体产品基岛与塑封料结合面积大幅度增加,同时发生基岛区域分层的风险同步增加。引线框架基岛设计中综合考虑了各类影响因素,汇总后如表 2 所示。

1.3 物料设计

不同厂家的各种物料之间结构和成份不同,在实际生产过程中会发生不同的物理、化学反应,即最优良的材料之间也可能因为不相互匹配造成产品出现分层问题。

上述物料间匹配问题在多芯片产品中更为明显,物料选择过程中需要做好充分的试验验证,避免物料之间匹配问题造成产品分层问题。

2 工艺过程设计

2.1 生产过程控制

生产过程中对于分层问题管控主要通过避免引线框架氧化、提高引线框架表面清洁度以及减少产品在车间的滞留时间进行控制。多芯片 ESOP 封装集成电路产品生产过程中需要多次上芯片和引线键合,因此需要进行特殊的工艺流程,降低产品滞留吸潮和污染分层风险。表 3 中除了正常的工艺时间管控外,多芯片 ESOP 封装集成电路增加了特殊的工艺要求。

2.2 生产过程分层监控

实际生产中存在各类的变化过程,需要在各个生产关键环节进行分层问题监控。表 4 列出了各个关键环节的分层监控管控要求。

3 实际分层问题分析和改善

3.1 集成电路分层问题描述

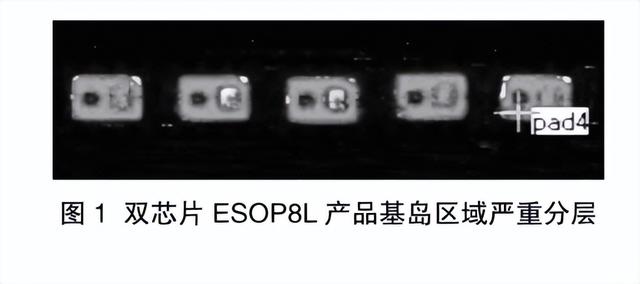

图 1 中双芯片 ESOP8L 集成电路产品出现不稳定的基岛区域严重分层问题,造成基岛区域 MOS 芯片与基岛脱离,集成电路产品整体失效。

3.2 产品、工艺设计以及产线生产排查

对图 1 中集成电路产品分层问题进行排查,排查过程如表 5 所示。

3.3 改善方案

根据表 5 中分析的排查问题点进行改善,改善方案如表 6 所示。

3.4 产品验证方案设计及效果确认

3.4.1 验证极限条件选择

验证过程若采用常规的生产条件,例如固晶胶处于使用寿命初中期、塑封料一次醒料、产品在产线流通速度很快等,未能涉及到生产的各个临界环节,进而没有验证整体产品的上限分层承受能力。本次验证过程中采用表 7 所示的极限生产条件,可以有效地确保集成电路产品的可靠性能。

3.4.2 验证方案及效果

选取同型号双芯片 ESOP8L 集成电路芯片分别选择改善前表 5 和改善后表 6 中设计条件,验证过程采用表 7 中极限生产过程。上述验证及效果确认如表 8 所示,通过验证确认改善方案有效,改善前方案存在分层风险。

4 分层可靠性验证的风险分析

4.1 验证通过产品的分层风险

一般分层可靠性评估选用 MSL3 以及可靠性试验后分层扫描进行判断。实际 MSL3 考核中绝大部分材料均可通过验证评估,而可靠性试验中比较严苛的温度是 150℃,温度比回流焊时的 260℃有一定差距。通过上述验证评估的多芯片 ESOP 封装集成电路产品,在长期生产过程中也出现过制程不稳定现象,造成一定的分层问题投诉。

发生上述情况的原因,一方面是验证过程未能涉及到生产的各个临界环节,实际生产和客户应用端均需要保留一定的余量,客户应用端也存在不规范使用情况,因此需要验证集成电路产品的极限应用条件。

另外一方面受限制于试验分析条件,例如分层扫描设备探头的频率差异、没有配备 T-SAM配件等。图 2 是不同频率探头对应的集成电路厚度范围图,当使用不适用的扫描探头时,也可能造成分层结果的误判。

由于分层扫描探头频率造成的分辨率影响,实际发生轻微分层可能不被设备识别到;另外芯片固晶胶底部的分层问题需要使用 T-SAM 进行扫描,需要额外增加十余万设备备件费用。上述分层扫描设备的限制,可以通过开盖后芯片推力试验进行判断,当固晶胶底部出现分层问题时,芯片轻推掉落或者推力值不满足规范要求,图 3 是开盖后进行的芯片推力测试。

4.2 基岛分层产品的风险分析

多芯片 ESOP 集成电路基岛区域发生分层时,产品失效的主要风险来自于芯片固晶胶水区域分层,造成芯片与基岛电路连接失效和散热能力降低,其它包括键合区域的失效与分层没有绝对的关联性。例如图 4 中基岛整体区域分层,实际开盖后图 5方框分层部分键合焊线正常,未发生脱落。

因此多芯片 ESOP 集成电路抗分层能力的设计主要偏重于固晶胶水部分。表 9 中通过普通固晶胶与高温固晶胶进行验证,在基岛区域分层情况,高温固晶胶产品仍然可以正常使用,开盖后固晶胶有一定推力,基岛区域有固晶胶残留。

5 结论

随着集成电路高密度、多功能、大功率等要求的提高,多芯片 ESOP 封装集成电路产品应用范围越来越广,对集成电路可靠性能提出更高要求;上述多芯片 ESOP 封装集成电路产品分层问题研究中,从理论到实际验证过程中,试验设计需要考虑综合的多种影响因素,找出验证产品的能力上限,避免生产中个别因素造成产品质量问题。