本文部分内容转载自《信号完整性》公众号

高速PCB设计有很多比较考究的点,包括常规的设计要求、信号完整性的要求、电源完整性的要求、EMC的要求、特殊设计要求等等。本文主要是针对高速电路信号总线做了一些比较常规的要求列举了一些检查要点,其实还可以进一步的细化,比如针对1.6mm板厚的设计,使用的diff-end via的结构是8mil的drill,16mil的pad,40mil的anti-pad,36mil的via间距。这都需要根据实际的情况而定。所以网上很多经验法则都是仅供参考的,包括本文也是如此。

随着信号速率的提升,电子产品设计也是越来越复杂。无论设计的能力有多强、设计经验多丰富,总会出现一些意想不到的问题。所以很多公司,都会有一些设计规则,让大家在设计中有据可依,也可以在设计完成之后作为checklist,一步一步地检查。下面列举了一些在信号完整性以及电源完整性中需要检查的点:

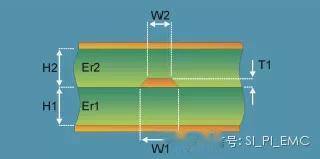

1、阻抗是否满足设计要求,这主要根据传输线的结构检查确认。不同的总线有不一样的需求。

2、高速信号线尽量不要跨分割布线。

微带线需要考虑一个参考平面。

带状线需要考虑两边,两个参考平面。

有时有的工程师认为有一个参考平面比较远,就忽略了跨风割带来的影响:

在 PCB 设计过程中,由于平面的分割,可能会导致信号参考平面不连续,对于低低频信号,可能没什么关系,而在高频数字系统中,高频信号以参考平面作返回路径,即回流路径,如果参考ᒣ面不连续,信号跨分割,这就会带来诸多的问题,如 EMI、串扰等问题。这种情况下,需要对分割进行缝补,为信号提供较短的回流通路,常见的处理方式有添加缝补电容和跨线桥接:

A. 缝补电容Stiching Capacitor˖通常在信号跨分割处摆放一个 0402 或者 0603封装的瓷片电容,电容的容值在 0.01uF 或者是 0.1 uF,如果空间允许,可以多添加几个䘉样的电容˗同时尽量保证信号线在缝补电容 200mil 范围内,距离越小越好˗而电容两端的网络分别对应信号穿过的参考平面的网络,见图一中电容两端连接的网络,两种颜色高亮的两种不同网络:

B. 跨线桥接˖常见的就是在信号层对跨分割的‘信号包地处理’,也可能包的是其他网络的信号线,这个个‘包地线’尽量粗,这种处理方式,参考下图

3、拓扑结构是否满足设计要求,对于SerDes总线,基本都是采用的点对点的设计结构,但是对于Memory,会涉及到T-type和Fly-by结构的选择,以及拓扑结构中每一段传输线的结构。

4、差分对内等长是否满足要求。对于速率特别高的总线,尽量满足等相位或者等时的要求。

5、对于特定的总线,其对与对之间等长是否满足要求。

6、高速信号网络不要布在板边,在比较大的散热通道附近也不要有高速信号线。

7、信号线与信号之间的距离是否足够大,使串扰足够小。

8、如果要给高速信号网络包地线保护,那么要有足够的距离(3W),避免因为包地导致新的信号完整性问题。

9、发送端与接收端的信号线距离尽量远,能分层布线最好。

10、在高速电路的PCB板中不要出现浮铜,要么去掉,要么在浮铜上加GND via。

11、高速信号网络的via不易过多,一般除了BGA或者Connector处,其它区域不超过1个,最差不超过2个via,同时要优化via到比较合适的大小。

12、观察高速信号的stub是否足够短,是否需要使用Back-drill。

13、高速信号线在换层时,其via附近是否有伴随GND Via。

14、如果信号线有冗余设计,要确保传输线的stub要足够短,尽量减少信号完整性问题。

15、参考平面要满足10H

参考平面虽然有了,但是需要满足高速信号在参考平面内侧,间距达到10H,H为层间间距。有时达不到,至少要按照3H来设计。

16、要满足阻抗连续

尽可能避免线宽突变

避免多个过孔

避免焊盘导致的阻抗变化,通过隔层参考、共面波导等措施来优化。

【1】兴趣驱动热爱

【2】硬件工程师要不要自己画PCB

【3】PCB走线应该走多长?

【4】PCB走线应该走多宽?

【5】PCB的内电层

【6】过孔

【7】PCB能不能走锐角和直角?

【8】死铜是否要保留?(PCB孤岛)

【9】焊盘上是否可以打过孔?

【10】PCB材料、FR4到底是指什么材料?

【11】阻焊层,绿油为什么多是绿色

【12】钢网

【13】预布局

【14】PCB布局、布线 的要领

【15】跨分割走线

【16】信号的反射

【17】脏信号

【18】沉金、镀金、喷锡等表面处理工艺

【19】线距

【20】电容的摆放位置

【21】串扰

【22】PCB的飞针测试

【23】FPC概述及仿真

【24】为什么PCB变形弯曲?如何解决?

【25】一文搞懂“特征阻抗”

【26】PCB的叠层设计

【27】高速电路PCB回流路径

【28】PCB设计中电源处理与平面分割

【29】锯齿形的PCB走线——Tabbed routing

【30】PCB的介质损耗角是什么“∠”?

【31】PCB铜箔粗糙度对高速信号的影响

【32】晶振为什么不能放置在PCB边缘?

【33】什么是高速信号?

【34】什么是传输线

【35】预加重、去加重和均衡

【36】如何利用PCB散热

【37】PCB设计中的“stub”

【38】纠结:走线之间的GND保护地线要还是不要?

【39】PCB 覆铜

【40】进行 PCB 设计时应该遵循的规则

【41】PCB叠层设计中的“假八层”

【42】除了带状线、微带线,还有“共面波导”

【43】PCB焊盘设计工艺的相关参数

【44】PCB设计时,板边为什么要打地孔

【45】更容易散热的PCB:铝基板

【46】为什么要把参考平面掏空?

【47】晶振的PCB设计

【48】用EMC思想来设计DC/DC电源的PCB

【49】PCB拐弯,不一定是圆弧走线最好

【50】为什么要把过孔堵上“导电孔塞孔工艺”

【51】电源PCB布局布线要点

【52】PCB板上的Mark点【53】用ADS仿真高速信号跨分割【54】刚柔板(软硬结合板)

【55】数模混合的PCB设计

【56】PCB设计中电容的摆放

【57】PCB设计中过孔残桩的影响

【58】PCB设计checklist:结构

【59】PCB设计checklist:电源

【60】PCB设计checklist:布线

硬十已出版书籍

《DCDC电源篇》正在走出版流程,预计5月份发售,敬请期待