随着半导体工艺复杂度提升,可靠性要求与测试成本及时间之间的矛盾日益凸显。晶圆级可靠性(Wafer Level Reliability, WLR)技术通过直接在未封装晶圆上施加加速应力,实现快速、低成本的可靠性评估,成为工艺开发的关键工具,本文分述如下:

晶圆级可靠性(WLR)技术概述

晶圆级电迁移评价技术

自加热恒温电迁移试验步骤详述

1

晶圆级可靠性(WLR)技术概述

WLR技术核心优势

无需封装:热阻低,允许施加更高温度和大电流密度而不引入新失效机理;

实时反馈:与工艺开发流程深度融合,工艺调整后可立即通过测试反馈评估可靠性影响;

行业标准化:主流厂商均发布WLR技术报告,推动其成为工艺验证的通用方法。

WLR技术的核心目标与应用场景

本质目标:评估工艺稳健性,削弱本征磨损机理(如电迁移、氧化层击穿),降低量产风险,并为工艺优化提供早期预警。

应用场景:新工艺或新技术开发阶段,快速识别潜在可靠性问题;与传统封装级测试结合,实现全周期可靠性评估与寿命预测。

关键测试领域与失效机理

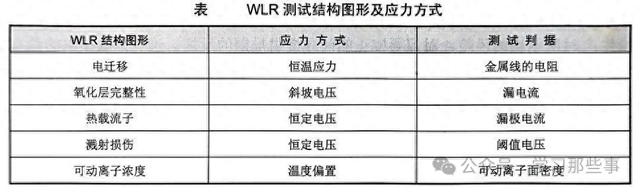

WLR技术聚焦半导体器件的本征可靠性,覆盖以下核心领域:

金属化可靠性——电迁移:互连测试结构监测通孔和有源区连接孔在电流应力下的失效。

氧化层完整性:测试结构检测氧化层因缺陷或高电场导致的击穿。

热载流子注入:评估MOS管和双极晶体管绝缘层因载流子注入导致的阈值电压漂移、漏电流增大。

连接可靠性——键合完整性:检测金属层与硅界面在高温或机械应力下的剥离或腐蚀。

其他失效机理:等离子损伤(天线效应),溅射工艺中电荷积累对栅氧化层的损伤;可动离子沾污,离子污染导致阈值电压下降;层间介质完整性,低介电常数(low-k)材料在应力下的击穿风险。

典型测试方法与结构

针对不同失效机理,WLR需设计专用测试结构并施加特定应力:

1.金属化完整性测试

测试结构:蛇形金属线或通孔链;

应力条件:高温(>150℃)与大电流密度(>1×10⁶ A/cm²);

监测参数:电阻变化率或开路/短路故障。

2.氧化层完整性测试

测试结构:电容结构(MOS电容或MIM电容);

应力条件:恒定电压(如5V)或电场(>5 MV/cm);

监测参数:漏电流激增或击穿时间(Time-to-Breakdown, TTB)。

3.热载流子注入测试

测试结构:NMOS/PMOS晶体管;

应力条件:高温(125℃)与高栅压(如1.5×工作电压);

监测参数:阈值电压偏)、亚阈值斜率退化。

4.可动离子沾污测试

测试结构:晶体管阵列;

应力条件:高温烘焙(如175℃)或反向偏压;

监测参数:阈值电压瞬时漂移。

5.溅射损伤测试

测试结构:栅氧化层直接连接金属互连线;

应力条件:模拟溅射过程中的电荷积累;

监测参数:氧化层击穿电压或漏电流。

WLR技术的科学性与优势

加速试验设计:通过提高应力强度(温度、电压、电流)缩短失效时间,建立失效模型外推至实际工作条件。

统计工艺控制(SPC):基于大量晶圆数据,量化工艺波动对可靠性的影响,实现早期缺陷筛查。

与传统测试对比:

速度:无需封装,测试周期从数周缩短至数小时;

成本:避免封装成本与测试设备损耗;

灵敏度:直接暴露工艺本征缺陷,避免封装材料干扰。

晶圆级可靠性技术通过实时、高效的在线监测,将可靠性评估深度融入工艺开发流程,显著加速了技术迭代并降低了量产风险。其科学化的测试设计与行业标准化趋势,使其成为半导体制造中不可或缺的可靠性保障手段。

2

晶圆级电迁移评价技术

电迁移是半导体器件中金属互连和通孔失效的主要机理之一。为评估其可靠性,传统方法依赖封装级测试,但存在效率低、成本高的问题。晶圆级技术的发展为电迁移评价提供了更高效、精准的解决方案。以下是关键技术的分述:

传统封装法

原理:将封装后的样品置于高温炉中,通入恒定电流,监测电阻变化。当电阻变化超过阈值时判定为失效,失效时间即为加速条件下的电迁移寿命。

缺点:耗时长,封装过程复杂,测试周期长达数周;电流限制,为避免焦耳热干扰炉温测量,电流密度需控制在较低水平(如<1×10⁵ A/cm²),进一步延长测试时间;温度不确定性,金属线自热导致实际温度高于炉温,影响结果准确性。

自加热法(晶圆级)

原理:利用金属线自身的焦耳热升温,通过电阻温度系数(TCR)实时计算金属线温度。通过调节电流控制温度,无需封装即可在晶圆级进行测试。

优势:高效性,省去封装步骤,测试周期缩短至小时级;精准控温,直接关联电流与温度,避免外部加热源干扰。

局限性——通孔测试失效:通孔与金属线界面因电流集中导致局部过热,无法准确测定整体结构温度。

多晶硅加热法

原理:在测试结构中集成多晶硅电阻作为加热元件,通过多晶硅通电流产生热量,间接加热电迁移测试区域(如通孔)。多晶硅充当“片上炉子”,通过优化版图设计(如多晶硅宽度、通孔数量)实现均匀加热。

优势:解决通孔测试难题,避免电流直接通过通孔,消除界面过热问题;灵活控温,通过多晶硅电阻设计调节加热功率。

挑战:版图设计复杂,需精确控制多晶硅尺寸与通孔布局以确保温度均匀性;工艺敏感性,多晶硅电阻值受工艺波动影响,需严格工艺控制。

Black方程与寿命外推

上述方法均在加速应力条件下测试,需通过物理模型外推至实际工作条件。

Black方程(上式),描述了电迁移寿命(t)与温度(T)、电流密度(J)的关系。其中,Ea为激活能,n为电流密度因子(通常取2),k为玻尔兹曼常数。

焦耳热修正:晶圆级测试中,大电流导致金属线温升

其中,T0为初始温度,R为电阻,ρ为电阻率,Δ为热阻。将修正温度代入Black方程,可更精准预测实际工作条件下的电迁移寿命。

意义:加速因子分离,明确温度(主导)与电流(次要)对寿命的影响;设计规则优化,通过外推结果,指导金属线宽度、通孔尺寸等工艺参数设计。

技术对比与演进

晶圆级电迁移评价技术通过自加热和多晶硅加热法克服了传统封装法的效率瓶颈,结合Black方程实现了从加速测试到实际寿命的精准预测,为半导体工艺可靠性优化提供了科学支撑。

3

自加热恒温电迁移试验步骤详述

自加热恒温电迁移试验基于JEDEC JESD61标准设计,通过一维热流模型模拟金属线温度分布,核心目标是加速电迁移失效并量化寿命。

具体实验步骤

试验分为四阶段,结合动态电流调节与温度反馈控制。

1. 初始测试阶段

目的:确定金属线初始电阻值(R0)及电阻温度系数(TCR),为后续温度计算提供基准。

操作:电阻测量,在恒温条件下(如室温)施加小电流(避免自热),测量金属线初始电阻R0;TCR标定:通过温度扫描实验(如变温箱控制),建立电阻随温度变化的线性关系

2. 电流上升测试阶段

目的:逐步增加电流,计算热阻并监测有效温度,确保温度趋近目标值。

操作:电流斜坡施加,以恒定速率(如10 mA/s)提升电流,每步平台处测量电阻R。

热阻计算:利用公式估算局部温度。

终止条件:当有效温度达目标温度的80%时,结束该阶段。

3. 温度收敛阶段

目的:通过算法优化电流调节,使金属线温度精准收敛至目标值。

操作:收敛级数算法,采用动态电流增幅控制(如逐步减小电流调整步长),替代传统差分热阻法,避免温度过冲。

实时反馈:基于电阻测量值(R(T))与TCR模型,动态调整电流以逼近目标温度Ttarget。

4. 恒定功率维持阶段

目的:在目标温度下持续监测电阻变化,直至失效发生。

操作:功率控制:根据初始目标温度下的电阻值Rtarget,调节电流使输入功率(P=I2R)恒定。

失效判据:电阻阈值:电阻值超过初始值的120%(Rfail≥1.2⋅Rinitial)。

实时终止:若电阻突增或开路,立即停止测试并记录时间。

关键参数与注意事项

电流密度范围:典型值1×10⁶~3×10⁷ A/cm²(对应10~300 mA/μm²),需根据金属线宽度调整。

反馈控制频率:控制周期≤500 ms(平衡精度与响应速度),最小周期≥50 ms(匹配热时间常数)。

失效时间定义:斜坡/收敛阶段失效:记为0时间失效(因未达目标温度)。

恒定阶段失效:记录实际时间,未失效样品需结合对数正态分布统计处理。

试验后分析

失效模式观察:去除钝化层后,用扫描电镜(SEM)检查金属线空洞、挤出等电迁移特征。

寿命外推:结合Black方程,将加速条件下的失效时间外推至实际工作条件。

通过上述步骤,恒温电迁移试验实现了对金属互连可靠性的高效评估,为工艺优化提供数据支持。

半导体工程师

半导体行业动态,半导体经验分享,半导体成果交流,半导体信息发布。半导体培训/会议/活动,半导体社群,半导体从业者职业规划,芯片工程师成长历程。