片上网络 (NoC) 技术在系统级芯片 (SoC) 设计中的应用已被证实可以减少布线拥塞并降低功耗。现在,一种新的NoC瓦格化(NoC-enabled tiling)方法有助于加速开发、便于扩展、支持SoC的降功耗技术并可提高针对人工智能 (AI) 应用的SoC设计重用。在本文中,我们将假设 AI 包括机器学习 (ML) 和推理等用例。

软瓦格与硬瓦格

工程学中的一个挑战是,同一个术语可能被用来指代不同的事物。例如,术语“瓦格 (tile)”就具有多种含义。有些人将瓦格等同于芯粒 (chiplet),芯粒是独立的小型裸硅芯片 (die),实际使用时安装在普通硅衬底或有机衬底或中介层上。芯粒可以被认为是“硬瓦格”。

相比之下,许多SoC,包括那些用于AI应用的SoC,都采用处理单元 (processing elements, PE) 阵列,这可以被视为“软瓦格”。例如图 1 所描述的通用SoC。

图 1. 包含NPU的SoC的高级框图。

除了包含多个通用CPU的处理器集群,以及其他几个IP模块之外,SoC还可能包含专用处理器或硬件加速器:图1中的SoC包括了一个图像信号处理器 (ISP)、一个图形处理器 (GPU) 和一个专为高性能、低功耗AI处理而设计的神经处理单元 (NPU)。

NPU是由相同PE组成的一个阵列。在不远的过去,这些PE通常是以相对简单的乘积 (MAC) 函数实现的,其中MAC是指乘加运算。相比之下,如今的 SoC 通常包含多个通过内部 NoC 连接的 IP 的 PE。

手动实现软瓦格化

在本文讨论的常见SoC场景中,NoC可以在设计层次结构的多个级别中使用。例如,可以在顶层使用NoC来连接处理器集群、ISP、GPU、NPU和其他IP。NoC可以以各种拓扑结构实现,包括环形、星形、树形、网状等。即使在SoC层次结构的顶层,某些器件也可能使用多个 NoC拓扑结构。

如前文所述,NPU中的每个PE可以由多个IP组成,这些IP通过内部NoC连接。此外,NPU中的所有PE也可以使用NoC连接,通常以网状拓扑结构实现。

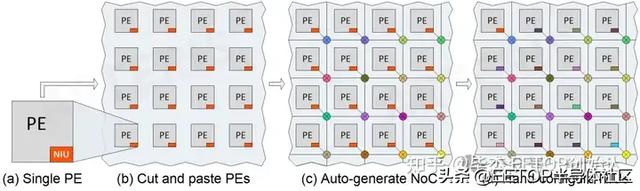

传统手工方法实现NPU是从创建单个PE开始的。除了AI加速器逻辑以外,PE还将包含一个或多个网络接口单元 (NIU),用于将PE连接到主网状NoC中。如图2a所示。

图 2. 手动实现软瓦格化。

如果我们假设NPU规范需要一个 4x4 的PE阵列,那么设计人员将使用“剪切-粘贴”方法将PE复制 16 次 (图2b)。接下来,使用NoC工具自动生成NoC (图2c)。在此过程中,NoC 生成器会自动为NoC的每个交换单元分配唯一标识符 (ID)。但是,PE中的NIU也将具有与PE相同的ID,即PE创建时的默认ID。

为了使NoC将数据从源节点传输到目标节点,每个PE中的NIU必须有一个唯一的ID。这需要设计人员手动修改每个 PE 实例,以便为每个NIU提供自己的ID。这一过程不仅耗时,而且容易出错,从而会影响下游测试和验证。

这种手动实现的瓦格化 (tiling) 技术面临一些挑战。例如,在设计过程的早期,经常会对PE规范进行更改。对于每次更改,设计人员有两种选择: (a) 在阵列的所有PE实例中手动复制更改,或者 (b) 仅修改原始PE,然后重复整个手动剪贴的软瓦格化过程。这两种方法都非常耗时且容易出错。

此外,手动执行软瓦格化也不方便扩展。如果需要用 8x8 版本替换原始的 4x4 阵列,例如用于衍生产品,则这个过程就会变得越来越繁琐,问题也会越来越多。

片上网络瓦格化

“片上网络瓦格化 (NoC-enabled tiling)”是SoC设计的一个新兴趋势。这种演进式方法采用成熟、稳健的NoC IP使扩展更容易、缩短设计时间、加快测试速度并降低设计风险。

使用片上网络瓦格化技术,设计人员也像以前一样从创建单个PE开始。不过,在这种情况下,可以使用NoC工具自动复制PE、生成NoC并配置PE中的NIU,所有这些操作只需几秒钟即可完成。设计人员只需要指定所需的阵列维度。

图3. 片上网络瓦格化技术

除了显著加快阵列生成过程外,这种“按照结构修正 (correct by construction)”的方法还消除了人为错误的可能性。它还使设计团队能够在SoC开发流程的早期快速、轻松地满足对PE的更改请求。此外,它还能极大地促进扩展和设计重用,包括创建衍生设计。

不断发展的市场

Arteris 与引领市场的创新者合作,共同应对不断发展的IP和SoC设计挑战。根据对客户目前正在开发的AI SoC设计的分析,Arteris 团队确定了软瓦格化在当今的 AI 关键垂直和水平领域中的相对使用情况。如图 4 所示,其中圆圈的面积反映了应用用例的相对数量。

图4. 当今AI在关键垂直和水平领域中片上网络瓦格化的使用情况。

总结

设计具数十亿个晶体管的SoC不仅十分耗时,而且面临许多挑战。一些SoC器件,比如针对AI 应用的SoC,可能包含由PE阵列组成的NPU等功能。

Arteris以其行业领先的一致性和非一致性NoC技术而闻名。片上网络瓦格化技术是一种新兴趋势,Arteris 公司领先的NoC IP产品和NoC工具给您带来先进的可靠的支持。我们还精心为您准备了Arteris 的三份技术白皮书,扫一扫二维码,即可获取如下资料。

扫一扫二维码,立即获取资料

资料清单

Arteris AI Tiling 总览Arteris FlexNoC 5 互联 IP 产品手册Arteris Ncore缓存一致性互联 IP 产品手册