2024年6月6日,英特尔发布了英特尔至强6能效核处理器,此次发布标志着英特尔首次将至强处理器拆分为性能核和能效核两个不同的分支。

其中,英特尔至强6的能效核已发布144核版本,随后明年Q1还会发布288核。而性能核的至强6也支持最高128核。

核数增多,不免让人担心内存墙的问题。

然而,至强6这次正式支持CXL 2.0,也就是可以支持内存扩展,它可以帮助解决内存墙的问题,让大家放心用上更多核心。

英特尔至强6产品路线图更新,144/288小核,128大核都要来了

6月6日,能效核版的英特尔至强6700E发布,最多核心数是144核,计划于2025年Q1发布的英特尔至强6900E核心数量将会来到惊人的288核。

性能核版本的英特尔至强6900P也将于今年第三季度择期发布,作为全性能核的处理器,其核心数量也将来到128核,与AMD第四代霄龙9754持平。

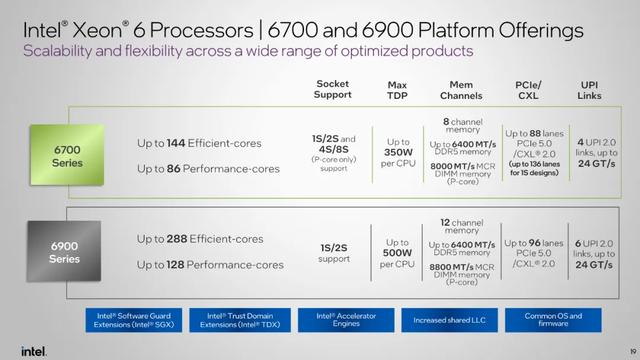

从上图可见,6700E支持单路和双路配置,最高350W的TDP设计,支持8个内存通道,内存速率从上一代的5600MT/s提高到了6400MT/s。它支持最多88个PCIe 5.0通道或者CXL 2.0通道。

全性能核的6700P,可以提供86个性能核,支持最高8路设计。默认支持8个内存通道,如果遇到对内存带宽要求更多的场景,还能使用至强6的MCR技术把内存速率提高到8000MT/s。

6900P则具有128个核心,比最多64核的第五代至强核心数翻倍。12通道的配置,搭配MCR技术提供的8800MT/s速率,其内存总体带宽达到上一代的2.36倍。

看来,至强6不只增加核心数量,其内存带宽的增加幅度更大,有助于解决内存墙问题。

值得注意的是,6900系列支持最多双路服务器配置,单台服务器最多576核或者256核。6900系列的TDP来到了最高500瓦,支持最多96个PCIe 5.0通道或者CXL 2.0通道,支持6个UPI 2.0链路,最高达到24GT/s的速度。

性能核和能效核的主要区别

性能核主要面向需要高性能和复杂计算的场景,具备更强的单线程性能和更高的指令集支持,适合AI和HPC等场景。能效核则针对高效能和高密度的计算需求,优化了每瓦性能,更适合微服务、网络和媒体处理等场景。

性能核微架构代号为Redwood Cove,每个核心具有2MB L2缓存,支持超线程技术。指令集支持AVX-512(2x512)和英特尔AMX,可用于AI和向量运算。每核心拥有64KB指令缓存和48KB数据缓存。此外,它支持512指令乱序执行引擎,能够更好地优化编程中的软件指令。

能效核规格有裁剪,其微架构代号为Crestmont,每四个单线程核心共享4MB L2缓存。指令集方面,支持增强版的AVX2(2x128),也可用于AI和向量运算。每核心拥有64KB指令缓存和32KB ECC数据缓存。它只支持256指令乱序执行引擎。

通过这些裁剪,每个能效核所占的面积大幅度降低,同时功耗也有所减少。这样就可以在同样的芯片面积或是功耗的框架下,提供更多的核心数量和更高的吞吐量。

英特尔至强6架构简介

第五代至强处理器采用了EMIB(嵌入式多芯片互连桥接)技术,由两个芯片组合而成。而英特尔至强6处理器的设计理念发生了变化,不再是简单地将芯片一分为二,而是按功能块进行划分。

如图所示,芯片中间是计算die,上下两部分是I/O die。I/O die主要处理高速I/O相关事务,要求不高,因此采用了成熟的Intel 7工艺。计算die需要高计算密度和核心逻辑密度,因此采用了最新的Intel 3制程工艺。

至强6700能效核的版本采用一个计算die和两个I/O die的设计。三个性能核产品,HCC(中核心数)为46核,LCC(低核心数)最少,只有16核。XCC(高核心数)为86核,中间有两个计算die。

至强6900的能效核版本也采用了2个计算die和两个I/O die的设计,核心数来到了288个。性能核版本放了3个计算die,核心数来到了128个。

英特尔强调,这种模块化设计的关键在于Fabric技术,可以将计算die和I/O die有机结合,通过高密度的EMIB桥接技术,实现die之间1TB/s带宽的无损通信,构建更强的通路系统。这种设计不仅优化了数据传输效率,还大幅提升了处理器的功能和性能。

计算die的中间是核心部分(Core),包括L1和L2缓存,CHA(缓存和内存访问控制),LLC(L3缓存),以及横向和纵向的Mesh Fabric。

另外,DDR或MCR内存控制器位于die的两侧。这种设计使得每个计算die内部的核心、缓存和内存访问都在较小延迟范围内完成。

I/O die的结构也通过Fabric和EMIB技术与计算die相连。所有芯片采用统一的I/O die架构,使得平台验证和软件使能更加高效。这种设计通过可复用的投入,实现了整个产品系列的高效开发和验证。

英特尔至强6正式支持内存扩展

英特尔在其至强6处理器中引入了CXL 2.0技术,CXL 2.0提供对Type 3设备的支持,也就是大家期待已久的CXL内存扩展设备,在具体实施层面,英特尔提供了三种内存扩展模式:

在CXL Numa Node模式下,系统的标准DRAM内存和通过CXL技术扩展的内存被视为两个独立的Numa节点进行控制。每个Numa节点都有自己的内存地址空间,系统软件或应用程序可以将任务分配到不同的Numa节点,从而优化内存的使用。

CXL Numa Node模式适用于需要精细内存管理的应用,可以通过操作系统、虚拟机管理程序(Hypervisor)或应用程序本身来辅助分层管理内存。

异构交织模式(Hetero Interleaved Mode)通过以硬件为基础的内存交织技术,将系统的DRAM内存和CXL内存混合在一起,形成一个统一的Numa节点。每个内存地址空间中的数据可以交替存储在DRAM和CXL内存中,从而均衡内存带宽,减少延迟。

异构交织模式适用于对内存带宽有高需求的应用,特别是当需要将DRAM和CXL内存结合使用时。此模式只有在配备性能核(P-core)的至强6700和6900处理器上才支持。

在Flat Memory模式下,CXL内存和DRAM内存被视为单一的内存层,操作系统可以直接访问这一统一的内存地址空间。硬件辅助的分层管理可以确保常用数据优先存储在DRAM中,次要数据存储在CXL内存中,从而最大限度地提升内存使用效率。

Flat Memory模式适用于希望利用CXL内存扩展而无需修改软件的应用。这种模式适用于所有的至强6处理器。

通过这三种模式,英特尔至强6处理器为不同的应用场景提供了灵活且高效的内存解决方案。

上图展示的是至强6处理器运行在MongoDB数据库时的性能差异,对比的变量是标准DDR5内存与CXL 2.0平面存储器模式。评估结果显示,在数据容量为125GB、256GB和512GB时,两者的性能差距分别仅为1%、2%和5%。

结束语

144核、288核,以及128核,更多的核心固然诱人,但内存墙的问题不得不重视。

英特尔至强6处理器不仅支持MCR,最高内存通道数也来到了12个,搭配用来解决内存墙问题的CXL内存扩展技术,内存墙的问题得到了有效针对。