本文由半导体产业纵横(ID:ICVIEWS)编译自eetimes

拆解2024年发布的处理器,考虑Chiplet是否真的合理应用。

通过实现半导体的微型化,并在更小的空间内集成它们,可以显著降低信号传输的延迟时间。同时,信号传输所需的充放电和驱动能力也随之减少,进而达到降低能耗的目的。

在过去的十年中,将处理器与内存集成至单一封装内的技术,如MCP(多芯片封装)、SIP(系统级封装)和POP(封装叠层技术),在消费电子领域(尤其是智能手机和相机)以及汽车领域(特别是在信息娱乐系统中)获得了广泛的应用。

与采用独立封装的产品相比,将两片或多片硅片组合并封装在一起,无论是在平放还是堆叠配置下,都能实现更小的体积。

最终,封装内部的布线结构趋于复杂化(具体而言,这包括了成本增加的因素,如封装内部布线层数的提升以及布线宽度和空间的缩减)。此外,由于位扩展、通道数量的增加、电源加固等因素,封装端子的数量显著增多,封装端子的球尺寸也显著减小。

截至2024年,chiplet(小芯片)一词在半导体行业新闻中频繁出现。据称,小芯片的优势在于其能够以较小的体积存储硅,并以可扩展的方式进行部署。然而,这可能会导致硅面积的增加,并且增加制造小芯片的工作量,这些小芯片需要能够作为单个硅芯片,甚至作为具有良好市场表现的系统级封装(SIP)来使用。

苹果 Vision Pro图1展示了2024年2月发布的“Apple Vision Pro”所搭载的真实图像(及音频)处理器“Apple R1”。如图所示,该处理器采用了由11个硅片组成的chiplet架构。初看之下,似乎仅有11个硅电容,然而在拆解后可以发现,电路表面实际上嵌入了额外的硅电容,共计17个,这些电容负责提供稳定的电源供应。

这种设计体现了对硅片的精妙布局。通过将处理器、多层存储器以及有助于提升性能的电容器等关键组件分解为更小的芯片,实现了功能与性能的优化。这一小型化过程使得这些芯片完美地契合于“Vision Pro”的内部结构。

图1:2024年2月发布的Apple Vision Pro处理器“R1”来源:Tekanarie Report

图2揭示了苹果公司在2024年9月推出的第十代智能手表Apple Watch Series 10内部的SIP(System In Package)封装结构。

自Apple Watch的初代产品起,苹果便采用了SIP技术,并在第十代产品中维持了与前代相似的尺寸,同时实现了功能的增强。该封装内大约包含20片硅片。其功能与两三代前的智能手机相当,包括通信、传感器、处理器、内存和接口等,然而其体积仅相当于一枚500日元硬币。

通信功能涵盖了LTE、UWB、Wi-Fi、蓝牙、NFC等,几乎囊括了日常生活中所需的所有通信方式。大约一半的核心功能由苹果公司采用其自研芯片实现。苹果在2019年收购了英特尔的LTE广域调制解调器业务部门,目前已发展成为一家全面拥有自主通信半导体技术的芯片制造商。

苹果自家研发的5G半导体预计将在2025年集成到产品中(尽管预计仍会与高通芯片并用)。得益于功能与性能的均衡,Apple Watch无需采用Chiplet技术。

图 2:Apple Watch Series 10 中安装的 SIP内部 来源:Tekanarie Report

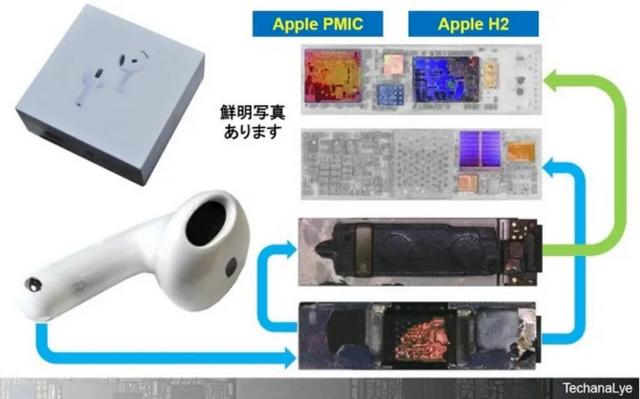

SIP也是耳机领域的竞争中心图3展示了苹果公司于2024年9月推出的第四代无线耳机“AirPods 4”。该系列耳机分为两款,一款具备主动降噪(ANC)功能,另一款则不具备。尽管两款型号在内部配置上保持一致,但它们的构造却各有特色。

其内部结构由驱动单元、电池以及系统级封装(SIP)构成。SIP内部巧妙地集成了八个硅胶组件和一个振荡器。此外,它还整合了五个核心半导体组件:存储器、模拟电路、传感器、通信模块、处理器以及电源管理单元。

两款耳机在功能上存在细微差异,但得益于市场上通用芯片的存在,通过采用SIP技术,相较于传统设计,其体积可缩减至约八分之一。可以肯定的是,若无SIP技术的运用,高级无线耳机的诞生将无从谈起。

图3:AirPods 4主板 来源:Tekanarie Report

表1展示了Apple、Sony以及Samsung Electronics推出的高端无线耳机产品。这些产品均采用了系统级封装(SIP)技术。SIP技术集成了多种芯片,包括但不限于通信、处理器、存储器、供电系统以及电池系统等。

除了硅芯片的应用,封装技术的进步对于先进无线耳机的实现同样至关重要。中国的半导体制造商同样采纳了SIP技术。

预计到2024年,将有4至5片硅芯片封装于单一封装内,并进行高级处理的情况将显著增长,这一点在Anker和华为的产品中尤为明显。封装技术不仅是无线耳机领域技术竞争的核心,也是推动行业发展的关键因素。

表1:高端耳机中使用的SIP 来源:Tekanarie Report

“智能Chiplet”和“临时Chiplet”图4展示了英特尔2024年发布的新系列PC处理器Core Ultra。英特尔已连续发布了三个 Core Ultra 系列(Meteor Lake、Lunar Lake、Arrow Lake,所有开发代号),并且都具有结合硅的小芯片配置。由于所有三个系列均适用于 PC,因此预计它们将拥有大量通用芯片。

图4:Intel Core Ultra的三种类型 来源:Tekanarie Report

表2概述了英特尔酷睿Ultra 3系列芯片的种类。该表未包含不具备功能晶体管的填充硅。英特尔目前正致力于开发12种不同类型的芯片,以构建这三个系列。这些芯片包括采用台积电不同工艺技术(3nm/5nm/6nm)的功能芯片,以及用于布线和供电的硅中介层,部分芯片源自英特尔自身的晶圆制造设施。

正如“Chiplet”一词所指,它代表了一个“混合组件”的集合。在表中,仅有一种硅胶(以浅蓝色标示)实现了标准化。此外,存在两种类型的小芯片,即“智能Chiplet”和“临时Chiplet”。目前,英特尔酷睿Ultra系列应被视为临时的Chiplet。

表2:三种Core Ultra的比较 来源:Tekanarie Report

图5展示了2023年英特尔酷睿系列的最终产品——英特尔酷睿i9处理器14900K、Arrow Lake与AMD计划于2024年第三季度推出的锐龙9000X系列的对比分析。

相较于采用单一硅片制造的14900K,采用Chiplet设计的Arrow Lake在硅片面积上需求翻倍,原因在于其底层硅中介层的面积亦有所增加。鉴于硅片面积与成本成正比,面积的成倍增长可被视为在硅材料使用上的倒退而非进步。

相对而言,AMD采取了更为精明的chiplet策略,仅对CPU芯片进行增减,通过chiplet技术区分不同性能等级的产品。

图5:Intel“Raptor Lake”和“Arrow Lake”与AMD“Ryzen 9000X系列”的硅片面积对比

高性能芯片图6揭示了2022年之后主要半导体制造商在超高性能芯片领域的现状。每家企业均采用其独特的制造工艺,然而在封装过程中,它们普遍采用包含大量硅片的设计。

CoWoS(晶圆上芯片封装技术)亦得到应用,有的企业完全采纳该技术,而有的则对其进行了部分调整。值得注意的是,各企业所采用的方法不尽相同。

实际上,许多技术并未在学术会议或企业宣传中公开,但通过拆解分析,这些技术的原理便能被轻易理解。

图6:主要半导体厂商的超高端芯片 来源:Tekanarie Report

图7显示了2024年发布的智能手机和PC使用InFO(集成扇出)技术的处理器的端子和硅电容器的数量。未来,将功能和特性整合到封装中将成为主流。

图 7:使用硅电容器的芯片示例 来源:Tekanarie Report

2025年,我也想通过观察“事物”(实际物体)来做出决定,我目睹了许多人不看最新案例就继续讲故事的案例。希望大家今年再次期待我们的产品拆解系列。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。