台积电又赢了,还是决定性的胜利。

12月6日,据中国台湾《经济日报》报道,台积电在新竹县的宝山工厂完成 2nm 制程晶圆的试生产工作。据有关报道称,此次试生产的良品率高达 60%,大幅超越了公司内部的预期目标。

根据台积电内部的研究人员称,和 2022 年推出的 N3(标称 3nm)工艺相比,N2 工艺预计将会在相同功率下,性能提升方面可以提高 10%至15%,而功耗降低25%至30%。

按照台积电董事长魏哲家曾在三季度法说会上的表态,2nm 制程的市场需求非常巨大,客户订单未来有一定的可能会多于 3nm 制程。

这次的2nm 制程,算是芯片发展的一个重大里程碑。

这一次的晶体管密度将会提升15%,也就是说台积电在半导体技术领域迎来了又一次飞升。台积电的2nm制程第一次引入GAAFET晶体管技术,运用能效更高的纳米片晶体管与互连,并和3DIC一起优化,主要用于AI、HPC和移动SoC应用。此外N2工艺还结合NanoFlex技术为芯片设计人员提供了之前从来没有过的标准元件灵活性。

除了台积电,英特尔也不甘人后。

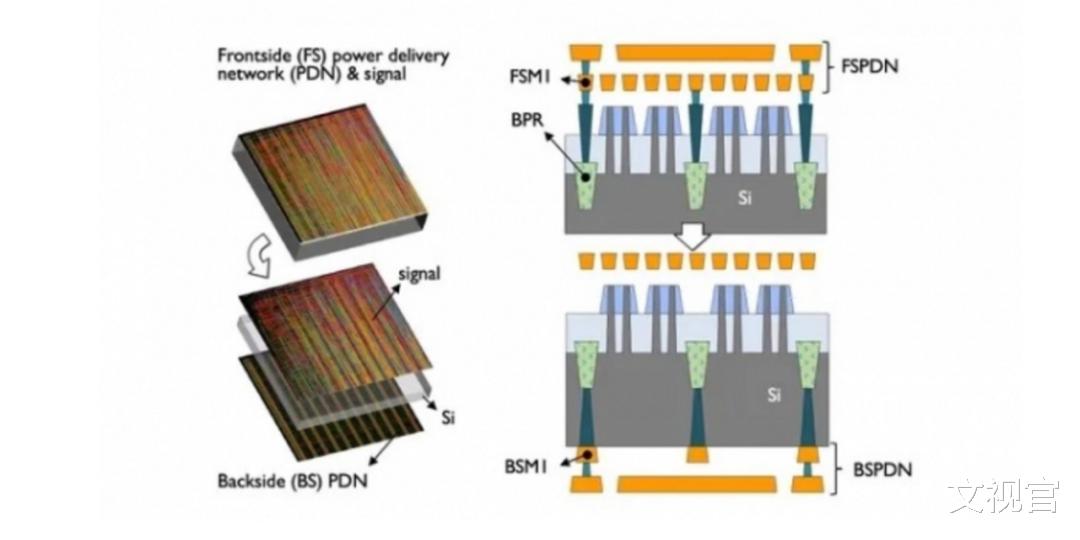

英特尔推出背面供电解决方案PowerVia。英特尔将背面供电(BSPDN) 确定为下一代 2nm 工艺节点的关键技术,业内都对英特尔背面供电的PowerVia解决方案的变革性影响表示非常期待。

其优点是非常多的。一方面背面供电将会提高芯片性能,另一方面还会提高电源效率并减少信号干扰,另外更要紧的是能可以使芯片变得更小,还有一方面是运用背面供电还能减少对配电层的需求,进而减少制造步骤总数并降低与半导体生产相关的成本。

据英特尔最近的 PowerVia 测试,让供电与信号路径分离可以显著提高单元利用率,甚至实现 90% 以上的效率。而PowerVia 的进步不单单限于电源效率。用 PowerVia 技术的测试芯片显示平台电压下降大大改善了,其数据是 30%,而频率性能提高了 6%。可以说用PowerVia 技术,英特尔方面很有希望能第一个实现实现背面供电技术的商业化。

反观三星却是屡战屡败,遇到了很大的危机。看起来三星先进半导体制造领域的其开拓者优势正在逐步消失。

在最为先进的3nm Gate-All-Around (GAA) FET 节点上,三星面临着各种业务上的挫折。因为三星心急,非常草率地直接在3nm工艺节点上就改成使用GAAFET架构。这种一步到位的决定受到了现实残酷的打击。因为于开发难度过大而且时间紧迫,3nm试生产的良率不足两成。

3nm 超低良品率始终让三星困扰,报告显示,这个节点只能生产出10%~20% 的可用硅片,这样的话目标客户几乎都不愿与三星建立合作关系。超低良品率同时还让三星出现的近三成的先进工艺设备闲置,这就导致低收益,这种情况就让使三星面临十分艰难的选择。

缺少订单和亏损不断增加使得三星实行节约成本的措施,其措施包含停止运营、缩减半导体工厂生产规模乃至推迟新设施的建设。

三星在3nm工艺制程上跌倒后,就下定决心要在2nm工艺制程上追赶他们。但按照三星电子的计划,其2nm产能至少到2027年才能实现量产。但是3nm工艺都让三星举步维艰了,更别说2nm了。

在3nm方面台积电可以说是没有敌手。台积电在研发3nm工艺制程的时候,并没有像三星一样一步到位立马改用GAAFET架构,反过来而是继续选择在FinFET结构上修修补补。可以说,台积电的技术是十分过硬的,从苹果的A17芯片开始,之前两年所有使用台积电3nm工艺代工的芯片都没有出现明显的发热或是高功耗的问题。

同时,因为FinFET工艺极其成熟,台积电全部从事3nm代工的产线,其良率都能达到八成以上,是指近乎九成。

对于三星只能说是心急吃不了热豆腐,台积电的匠心精神也不是一般人能学得来的,目前来说,在半导体行业,台积电的对手可以说是屈指可数。而在2nm工艺制程的开发上,台积电可以说是遥遥领先。