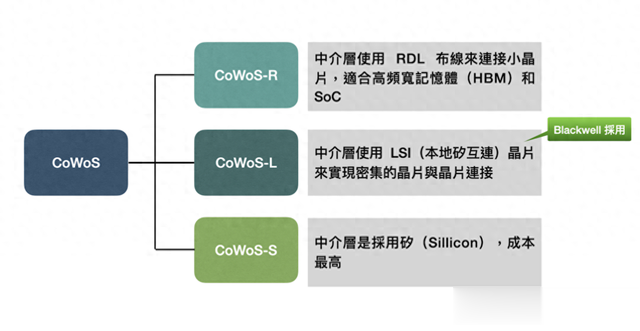

在摩尔定律事实上失效了以后,过往在单芯片上通过改善工艺制程来推高芯片性能的方式逐渐成为了过去式。取而代之的是各种先进封装技术,用各种“拼接”的方式去推高芯片的性能。这种趋势一个典型的范例就是GPU芯片巨头英伟达在最新的B200上的实践。 作为单芯片最忠实的支持者,英伟达过去多年里一直都是通过工艺和架构改善来提高芯片的性能,然而在B100上,英伟达也事实上采用了行业主推的Chiplet设计方式,用自有的NV-HBI(Nvidia High Bandwidth Interface)把两个突破了reticle极限的两个芯片连接起来,按照technews所说,在这背后倚仗的是台积电的CoWoS先进封装工艺。

事实上,从英伟达在GPU中引进HBM以及LLM的火热开始,先进封装就在高性能计算中名声大噪。如去年因为台积电COWOS先进封装制程产能短缺所引致的H100供给不足就引发了行业广泛讨论。对芯片性能需求的不断攀升也推动了先进封装技术的持续升级,也让大家对先进封装发展路线有了更多思考: 例如TCB(Thermocompression bonding)和混合键合(hybrid bonding)会如何发展? TCB,尚能饭否? 在详谈TCB之前,我们先对先进封装进行一个定义。其实关于什么是先进封装,不同行业有不同的定义,Semianalysis的分析师Dylan Patel就把所有凸块尺寸(bump size)小于 100 微米的封装称为“先进封装”。 他在文章中进一步指出,最常见的先进封装类型称为扇出型封装(Fan-out),在苹果公司将其应用到其A系列手机芯片后广为大众熟知。与传统倒装芯片封装相比,苹果芯片封装的凸块密度(bump density)大约高出 8 倍。而从构造上,除了常规的封装,现在先进封装有2.5D和3D封装。

所谓2.5D / 3D封装是在同一封装内包含多个 IC 的两种封装方法。在2.5D结构中,两个或多个有源半导体芯片并排放置在硅中介层上,以实现极高的芯片间互连密度。在 3D 结构中,有源芯片通过芯片堆叠进行集成,以实现最短的互连和最小的封装尺寸。 目前,2.5D是更多芯片厂商的首选。例如英伟达的H100 GPU采用的就是2.5D封装中最常见和产量最高的TSMC CoWoS(chip on wafer on substrate)。在这个封装方法中,台积电将把有源芯片封装在只有互连和微凸块的晶圆顶部,然后使用传统方法将这堆芯片封装到基板上。近年来大火的HBM则属于2.5D封装的另一个典型范例,在其生产过程中也使用了本章节我们讨论的技术重点——TCB。

作为引线键合(Wire Bonding)的一种主流方式,TCB是由贝尔实验室的三位科学家 O. L. Anderson、H. Christensen 和 P. Andreatch 在 1955-58 年期间开发完成的。 相关资料介绍,热压键合主要用于创建原子级金属键合。它利用力和热量来促进原子在晶格之间迁移,从而形成清洁、高导电性和坚固的键合。通常,TCB被用于垂直集成器件的 CMOS 工艺、金引线和表面之间固态键合的顺应键合(compliant bonding)、用于将芯片凸块键合到基板的倒装芯片应用以及用于连接微型组件的热压键合。 因为其应用的领先型,在发布了以后,这类封装的需求也很大。这个技术也在过去几十年里也一直在封装市场“呼风唤雨”,即使在文章开头谈到的HBM,无论是三星、SKHynix 和美光供应的产品,都也使用了TCB技术。 作为一种创新型的DRAM,HBM在过去几年大放异彩。就连英伟达CEO黄仁勋在日前举办的GTC大会上谈到HBM的时候,也直说这是一个技术奇迹。 从技术层面上看,HBM的为了将内存带宽提高到传统 DRAM 之上的一种方式。它通过使用更宽的内存总线来实现这一点。这些宽总线会产生与 IO 计数相关的问题,但 HBM 是从头开始设计的,可以在同一封装内共存,就这颠覆了 IO 问题,同时还允许更紧密的集成。

在Semianalysis分析师Dylan Patel看来,之所以当前的HBM还在用TCB,是因为这项技术解决了标准倒装芯片(standard flip chip)的几个主要问题。例如热量从芯片顶部施加,因此只有芯片和 C4 焊料连接会升温,可以最大限度地减少任何基板翘曲问题。同时,这种键合方式确保均匀粘合,没有间隙变化或倾斜;最后,这种粘合几乎没有空隙,也没有污染。 “在相同的 IO 间距下,TCB可实现更好的电气性能。TCB 还允许 IO 间距缩小到更小的尺寸。TCB 还可以封装更薄的dies和封装。后者正是是HBM使用TCB的原因。与标准倒装芯片工艺流程相比,TCB 似乎是一种更好的技术,”Dylan Patel接着说。

作为最早打造TCB解决方案的厂商之一,Kulicke & Soffa(库力索法)执行副总裁兼总经理张赞彬先生也告诉半导体行业观察:“在未来很长的一段时间以内,TCB也将在AI、HPC和大芯片中发挥非常重要的作用,关键的原因在于其成本优势。”“现在大部分芯片的Pitch都是50微米和30微米,最窄的为25微米,我们认为TCB可以做到10个微米以下,所以这条路还很长。”张赞彬接着说。 以HBM为例,张赞彬表示,目前HBM有两种实现方法:一个是用传统的flip chip去封装。另外一个是用TCB。其中前一种会一直存在,但如果需要温度控制,就用TCB。同时,因为HBM堆叠的die需要非常薄,所以直到现在最先进的12堆栈HBM,依然是使用了TCB技术。“从目前看来,下一代的16堆栈HBM,依然会使用TCB工艺。”张赞彬告诉笔者。 Dylan Patel在其文章中披露,Intel的大部分封装技术也使用TCB,并成为了TCB的坚定支持者,英特尔在许多封装应用中使用 TCB。又因为 TCB 是封装极薄芯片的最佳技术,因此 TCB 也在使用 OSAT 和 IDM 封装的旗舰设备中的手机应用中进行了试验。三星、高通/Amkor 也已在一些与层叠封装 (PoP) DRAM 相关的应用中使用了 TCB,OSAT也开始订购越来越多的 TCB 工具。 但正如Dylan Patel所说,厂商正在转向更神奇混合键合技术。 混合键合,未来可期 根据Dylan Patel的观点,封装行业最后一次重大范式转变是从引线键合到倒装芯片。从那时起,更先进的封装形式(例如晶圆级扇出和 TCB)一直是相同核心原理的渐进式改进。这些封装方法都使用某种带焊料的凸块作为硅与封装或板之间的互连。而这些技术可以一直缩小到约 20 微米的间距。 “但是,为了进一步扩展,我们需要另一种范式转变:采用混合键合的无凸块互连的混合键合,其尺寸超出了 10 微米互连间距,路线图为 100 纳米范围,并且它不使用任何中介物,例如具有更高电阻的焊料。”

所谓混合键合,是指在一个键合步骤中同时键合电介质(dielectric)和金属键合焊盘(metal bond pads)。具体而言,混合键合有两种类型:一种是晶圆到晶圆(wafer-to-wafer:W2W)键合,这种方式更加成熟,但限制了相同芯片尺寸的组合;另一种是芯片到晶圆(die-to-wafer:D2W)键合,它涉及更多的工艺步骤以及将芯片单独放置在载体晶圆或玻璃上(集体芯片到晶圆方法)。

在这两种情况下,通过 BEOL 金属化处理的两片晶圆都会经历键合电介质的 CVD、阻挡层的镶嵌沉积,然后铜填充、电介质的平坦化(带有轻微的铜凹进)、等离子体激活以准备键合、对准、室温键合,并退火以形成铜焊盘的电连接。然后将硅晶圆背面研磨至最终厚度(通常<100nm),之后切割,然后进行最终组装和封装。 与微凸块(microbumps)相比,过渡到混合键合的原因相当简单。那就是3D 内存堆栈和异构集成(超越摩尔时代的两个参与者)需要极高的互连密度,如上所述,混合键合可以满足这一需求;与本身支持高密度互连方案的微凸块相比,混合键合可提供更小尺寸的 I/O 端子和减小间距的互连。每个芯片之间的间隔距离取决于微凸块的高度,但在混合键合中该距离几乎为零。 因此,混合键合互连方案可以显著降低整体封装厚度,在多芯片堆叠封装中甚至可能高达数百微米。为此,自十多年前在 CMOS 图像传感器中首次亮相,混合键合逐渐走向了3D NAND,甚至连DRAM和HBM,也对混合键合产生了兴趣。今年二月更是有消息传出,英特尔下一代 Xeon“Clearwater Forest”CPU 采用一个名为“Foveros Direct”的混合键合的3D 堆叠技术。

有TCB支持者坦言,在凸块间距达到 25 微米后,还会继续使用已安装的 TCB 工具。张赞彬也认为,Hybrid Bonding只有在很高端应用才会用到。 “Hybrid Bonding是针对微纳米这种高端工艺的,这种技术不是每一种产品可以应用,因为它的价格和成本都很高,所以我觉得几种高端产品会有这种应用,大部分的芯片还是会用到传统的方法。”张赞彬说。他指出,和TCB是一个后段制程不一样,混合键合某种程度上是一个前道工艺,所以这带来的挑战也是显而易见的。 “混合键合对环境要求非常高,要达到class 1 clean room(非常的清洁),这是为什么现在目前投资Hybrid Bonding的大部分客户都是前端的客户,因为他们有前端的制程、设备和环境,所以可以扩大Hybrid Bonding。但是一个传统的封装厂如果想切入这个领域,则要做一个大投资,要做非常清洁的Clean room,这样的话门槛就提高了很多。这也是为什么打线机今天还那么受欢迎,因为在封装这方面是最实际、最便宜的方法。”张赞彬解析说。 最近的一则新闻,也让混合键合遭受了打击。 在去年12月举办的IEDM 2023上,SK海力士宣布,其已确保HBM制造中使用的混合键合工艺的可靠性。消息表示,HBM 芯片的标准厚度为 720 µm。预计将于 2026 年左右量产的第 6 代 HBM(HBM4)需要垂直堆叠 16 个 DRAM,这对当前的封装技术满足客户满意度来说是一个挑战。因此,Hybrid Bonding工艺在下一代HBM中的应用被业界认为是必然的。 但是,早前有消息透露,国际半导体标准组织(JEDEC)的主要参与者近日同意将HBM4产品的标准定为775微米,那就意味着HBM开发者使用现有的键合技术就可以充分实现16层DRAM堆叠HBM4。 不过,这应该不会阻挡厂商们投入这个赛道。据了解,包括台积电、英特尔、三星、SK海力士、美光、索尼、豪威科技、铠侠、西部数据、Besi、芝浦电子、东京电子、应用材料、EV Group、SUSS Microtec、SET和博世等厂商都对混合键合产生了兴趣。 甚至连TCB解决方案的主要供应商Kulicke & Soffa加入了混合键合阵营,对这个技术进行了预研,并认为这个技术在未来某个时刻迎来新的机会。 设备厂商,见招拆招 虽然有波折,但先进封装前进的道路是不可逆转的。 行业咨询机构Yole在去年年底发布的报告中表示,预计先进封装市场在 2023 年将下降 1.4%,但2023年Q3,先进封装(AP)营收较上季度大幅增长23.7%,总计达到110亿美元。 Yole进一步指出,在未来几年,先进封装收入预计将以 8.6% 的复合年增长率增长,从 2022 年的429亿美元增长到 2028 年的704亿美元。 就收入而言,倒装芯片 BGA、倒装芯片 CSP 和 2.5D/3D 是主导封装平台,其中 2.5D/3D 技术显示出最高的增长率,预计将从 2022 年的94亿美元增长到 2028 年的225亿美元,复合年增长率为 15.6%。

作为先进封装的主要实施者,设备厂商也正在见招拆招。 Kulicke & Soffa早在2015年就正式发布了其第一款TCB设备—APAMA系列,目前有APAMA PLUS和APTURA两大系列设备,可以实现目前大部分产品的TCB应用。 在早前举办的Semicon China,库力索法就带来了新一代APAMA PLUS热压焊接机和APTURA 无助焊剂热压焊接机。 首先看APAMA PLUS热压焊接机,库力索法表示,该设备主要用于手机应用芯片及硅光子量产, 能有效及快速解决封装制程中的翘曲问题并大幅提升良品率;至于全新的APTURA 无助焊剂热压焊接机,则能完全消除在超大晶片及超精细微型凸块助焊剂残留的问题, 并有助于异构集成及Chiplet的微型凸块从35µm焊接间距缩小到10µm, 让用于下一代人工智能、高性能计算HPC、高端服务器及数据中心的先进封装产品能够顺利量产。 值得一提的是,库力索法之前也曾表示,新型无助焊剂工艺消除了污染问题,同时通过独特的集成无助焊剂传输模块确保互连完整性。这一最新的高精度 TCB 平台能够支持大多数新兴的低至 10μm 的异构封装需求,正在引起公司无晶圆厂、代工厂、IDM 和 OSAT 客户群的极大兴趣。 此外,在本次展会上,K&S首次向市场展示其最新开发的晶圆级焊接垂直焊线工艺。该工艺针对存储器、射频、先进封装等产品应用,为电磁屏蔽提供更为经济可靠的线焊解决方案。 配合垂直焊线展示的ATPremier PLUS是目前业界速度最快的的晶圆级焊接机,能焊接300毫米晶圆、大尺寸基板和陶瓷;超细间距焊接可达到+/-3.5微米的焊接精度;配备K&S独有的结果导向工艺能扩展制程宽度、提升作业效率和产品可靠性。除了这些传统设备,库力索法在先进微点胶上的投入,也是公司面对先进封装未来的一个押宝。 据了解,点胶机主要协助各种的流体应用,具有应用层面广、技术门槛高、附加价值高、一广二高的特性,针对不同的制程需求,有不同的制程。包括消费性电子、绿能产业的太阳能板、电动车电池、光通讯产业、医疗产业、食品产业等都可以看到流体应用。 而具体到芯片封装领域,Kulicke & Soffa先进点胶事业部技术方案经理戴子祺以最基本的die bonding为例说道,在这种封装里面会有Die Attach的应用,而Die Attach下面就有导电胶和非导电胶。“在过去,die bonding通常会把点胶机整合在一起,但是一旦发现Substrate有翘曲的时候,那么整合的设备就应用不了,于是就需要寻求另外的微量控制的方案。 ”戴子祺告诉半导体行业观察。“尤其是在先进封装领域,微点胶方案的优势最为明显。”戴子祺补充说。 张赞彬也告诉笔者:“TCB的下一步就是underfill,这也是属于点胶的流程。而且随着TCB的增加,先进点胶需求也会同样一起增加。”他同时指出,库力索法在过去几年里一直在寻找和我们的先进封装相配合的业务,希望打造一个更完整的服务,以服务更多客户,并推动公司获得更多受益。恰好,通过在mini LED项目上与领先微点胶方案供应商高科晶捷的合作,最终促成了公司对后者的并购,进军点胶机市场。 按照库力索法所说,先进微点胶是新加入公司的一个事业部,专注于为先进封装、IC、汽车LED、光学传感器、功率模块、先进显示等市场提供从成本效益到高性能高精度的全方位智能点胶解决方案。 在本届SEMICON CHINA展会上,公司带来了拥有以下三个特点的SL型号点胶机: 一、设备占地面积小:宽幅仅有0.8米;二、高速高精度的制程:末端从线精度为+/-1微米;三、制程智能化: 点胶过程中可依据需求插入实时监测,设备能通过自检达到实时工艺优化,并依据来料形状和翘曲自动调试修正、特别是针对不透明材料,能搭配检测穿透材料量取內部结构。 “虽然传统设备的基本设计是很成熟也没有大改变,但是其应用越来越多。所以无论是铜线、铝线还是金线的传统打线机,现在应用越来越多。TCB也是同样的逻辑。”张赞彬说。正是基于这个观察,张赞彬认为半导体未来大有可为。