编者注:本文的内容其实比较简洁,前面两个因素结合ADS仿真原理图给大家介绍,有兴趣的也可以照着做做。很多总线都会给处损耗的要求,所以对于设计工程师而言,就需要哪些因素主导着损耗的变化。

我们经常讨论PCB中损耗大小的问题。有的工程师就会问,哪些因为会影响损耗的大小呢?其实,最常见的答案通常会说PCB材料的损耗因子、PCB传输线的长度、铜箔粗糙度,其实答案肯定远不至于此。下面我们分别就相应参数做一些实验给大家介绍下PCB板中哪些因素对传输线损耗有影响。

首先看看介质损耗因子Df对损耗的影响,以Df为变量,分析Df的变化对损耗的影响,下图是分析的原理图:

仿真对比结果如下,显然,随着PCB介质损耗因子的变大,损耗越来越大:

仿真对比结果如下,显然,随着PCB介质损耗因子的变大,损耗越来越大:

长度也是损耗的主要因素之一,把传输线长度设定为Len变量,分析Len的变化对损耗的影响,下图是分析的原理图:

仿真对比结果如下,显然,随着传输线长度越来越大大,损耗越来越大:

铜箔是PCB中常用的导体,其粗糙度的大小也会对损耗造成影响,通过分析,粗糙度的变化对损耗的影响如下图所示:

从上图中可以看到铜箔粗糙度越大,损耗越大。

这三个影响因子是工程师们很容易能理解。为了减小,工程师们通常想到的方式就是使用低介质损耗角因子、减短传输线长度以及减小铜箔粗糙度。

除了这三个影响因子,还有诸如过孔、传输线对内不等长、串扰等对损耗有影响。如高多层板中的过孔,很多时候都会存在的过孔残桩(Stub),如下图所示:

过孔残桩(Stub)就会导致损耗变大,如下图所示为相同的过孔,没有残桩和有残桩的损耗结果,有残桩的时,会存在一个非常大的谐振点,即在此谐振点处,损耗非常大。

并且,随着残桩越来越大,谐振的频率会越来越小(相对应在特定的频率处损耗也会变大)。

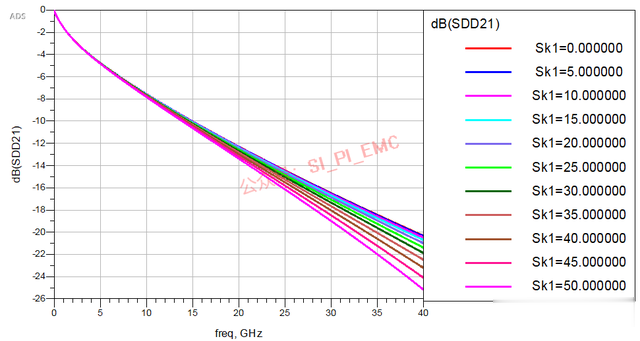

在PCB设计中,经常会出现差分对内不等长(偏差skew)的现象,经过实验发现,随着偏差长度的变化,损耗也会不一样。如下图所示,随着偏差长度的越来越长,相同频率点处的损耗也越来越大。

在集成度越来越高的产品设计中,串扰是工程师一直都在担心的问题。因为严重的串扰会导致很多信号完整性的问题,比如对损耗的影响就是其中之一。如下图所示为微带线时,当传输线与传输线的间距变化时的损耗对比结果。

显然,在保持其它设置不变时,间距越大,在相同特定频率点处,传输线的损耗衰减越小。其实串扰对损耗的影响还有一些比较有趣的现象,比如什么时候串扰会造成损耗的谐振点,等等。

以上几个因素对PCB传输线的损耗影响非常大。当然,还有一些其它的因素的实验结果后续有机会再给大家分享。大家也可以在文末留言共同讨论。

【2】硬件工程师要不要自己画PCB

【4】PCB走线应该走多宽?

【6】过孔

【8】死铜是否要保留?(PCB孤岛)

【10】PCB材料、FR4到底是指什么材料?

【12】钢网

【14】PCB布局、布线 的要领

【16】信号的反射

【18】沉金、镀金、喷锡等表面处理工艺

【20】电容的摆放位置

【22】PCB的飞针测试

【24】为什么PCB变形弯曲?如何解决?

【26】PCB的叠层设计

【28】PCB设计中电源处理与平面分割

【30】PCB的介质损耗角是什么“∠”?

【32】晶振为什么不能放置在PCB边缘?

【34】什么是传输线

【36】如何利用PCB散热

【38】纠结:走线之间的GND保护地线要还是不要?

【40】进行 PCB 设计时应该遵循的规则

【42】除了带状线、微带线,还有“共面波导”

【44】PCB设计时,板边为什么要打地孔

【46】为什么要把参考平面掏空?

【48】用EMC思想来设计DC/DC电源的PCB

【50】为什么要把过孔堵上“导电孔塞孔工艺”

【52】PCB板上的Mark点【54】刚柔板(软硬结合板)

【56】PCB设计中电容的摆放

【58】去耦电容在PCB设计中的布放与走线

【60】PCB设计checklist:电源

【62】PCB设计checklist:高速数字信号

【64】PCB设计:金手指

【66】DDR4的PCB设计及仿真

【68】什么是好的“PDN”的PCB设计

【70】USB2.0 PCB布线

【72】PCB设计,焊盘与过孔工艺规范

——硬件推荐书籍——