台积电已经明确表示,其2nm工艺制程开发进展顺利,预计将在2025年实现量产。具体来说,台积电在高雄的2nm新厂已经举行了设备进机典礼,并且时间线已经提前了半年,意味着全球2nm制造的时间表也向前推进了一步。因此,可以合理推测,台积电的2nm芯片有望在2025年下半年正式投入量产。

台积电2nm工艺采用了第一代纳米片晶体管技术,在性能与功耗方面实现了全面跨越。目前,主要客户已经完成2nm IP设计并开始验证。此外,台积电还开发出低阻值重置导线层、超高效能金属层间电容等技术,以进一步提升2nm制程工艺的能效。

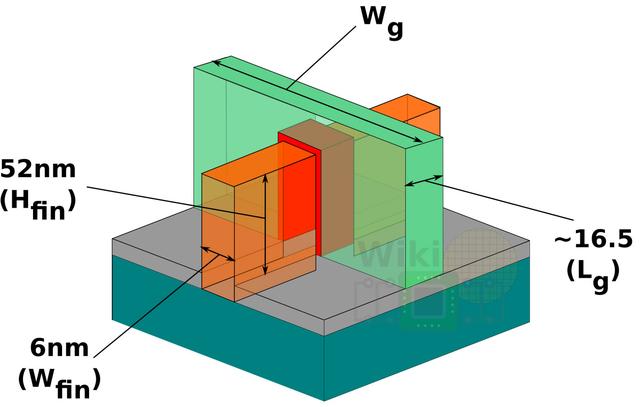

台积电2nm工艺首次引入了全环绕栅极(GAA)纳米片晶体管,这种新型晶体管结构有助于调整通道宽度,从而在性能与能效之间实现更好的平衡。GAA技术通过使栅极完全环绕通道,提高了栅极对通道中电子的控制能力,从而增强了晶体管的开关性能和能效。

相较于当前的3nm工艺,台积电2nm工艺在晶体管密度上实现了15%的提升。这意味着在相同的芯片面积下,可以集成更多的晶体管,从而提高计算能力和数据处理速度。

台积电2nm工艺在同等功耗下性能提升了15%,而在同等性能下功耗则降低了24%~35%。这一双重优化使得未来的芯片在保持高性能的同时,能够显著减少能耗,延长设备的电池续航时间。

台积电在2nm工艺中引入了NanoFlex DTCO(设计技术联合优化)。这一技术允许开发者在芯片设计阶段就进行精确的优化,以开发出面积最小化、能效增强的更矮单元,或者性能最大化的更高单元。

台积电2nm工艺还采用了第三代偶极子集成技术,包括N型和P型纳米片晶体管。这一技术使得工艺能够支持六个电压阈值档(6-Vt),范围在200mV。通过调整电压阈值,可以进一步优化晶体管的性能和能效。

台积电2nm工艺在静态随机存取存储器(SRAM)密度方面也取得了突破,使得未来的芯片能够集成更多的SRAM单元,从而提高数据存取速度和系统性能。

为了进一步提升芯片的能效和可靠性,台积电在2nm工艺中引入了全新的MOL中段工艺和BEOL后段工艺。这些新工艺的采用使得芯片的电阻降低了20%,从而提高了能效。

在台积电2nm工艺中,第一层金属层(M1)的制造流程得到了显著简化。现在,仅需一步蚀刻(1P1E)和一次EVU曝光即可完成M1层的制造。这一改进大大降低了制造的复杂度和光罩数量,从而提高了生产效率和降低成本。

针对高性能计算应用,台积电2nm工艺还引入了超高性能的SHP-MiM电容。这种电容的容量达到了每平方毫米200fF,能够支持更高的运行频率。

客户对于台积电2nm技术的兴趣超过了3nm,这一点在市场需求上得到了进一步印证。例如,苹果预计将成为台积电2nm技术的首批客户,计划将2nm工艺应用于未来的M5芯片和iPhone设备上。

台积电2nm工艺的发布将对半导体行业产生深远的影响。它将推动芯片制造商加快技术升级的步伐,以跟上台积电的步伐并保持竞争力。同时,2nm工艺的应用将加速电子产品向更高性能、更低功耗和更小尺寸的方向发展。

尽管台积电2nm工艺取得了显著的技术突破,但仍面临高能耗和成本上升等挑战。为了应对这些挑战,台积电正在积极寻求解决方案,包括在新竹科学园区的Fab 20工厂建立2nm生产基地,并计划扩展到台中科学园区,通过多阶段工程逐步提升良率和降低能耗。

从工厂分布来看,台积电在中国台湾已建成的工厂中,宝山的P1、P2以及新竹的F20、高雄的F22都将生产2nm芯片。这些工厂的建设和产能提升计划已经明确,为2nm量产的顺利进行奠定了坚实基础。

台积电的2nm芯片试产良率已经达到60%以上,这一数字远高于竞争对手,显示了台积电在2nm技术上的领先地位。

台积电作为半导体行业的领军企业,其2nm技术的成功研发将为中国芯片行业提供重要的技术示范。这将激励中国芯片企业加大研发投入,加快技术升级步伐,努力缩小与国际先进水平的差距。

台积电2nm技术的量产将带动整个半导体产业链的发展。中国芯片企业可以通过与台积电等领先企业的合作,共同推进材料、设备、制造等环节的技术进步和产业升级。这将有助于提升中国半导体产业的整体竞争力。

随着台积电2nm技术的量产,市场对高端芯片的需求将进一步增加。这将为中国芯片企业提供更多的市场机遇和发展空间。同时,台积电的成功也将加剧半导体行业的竞争格局,促使中国芯片企业不断提升自身实力以应对挑战。

在全球化背景下,中国芯片企业需要积极参与国际合作与竞争。台积电2nm技术的成功研发将为中国芯片企业提供与国际领先企业交流合作的机会,共同推动半导体技术的发展和创新。同时,中国芯片企业也需要加强自主研发和创新能力,以在激烈的国际竞争中立于不败之地。

台积电2nm技术的量产时间和研制进展已经明确,并且将对中国芯片行业产生深远的影响。中国芯片企业需要抓住机遇、迎接挑战,不断提升自身实力和技术水平以应对未来的市场竞争和技术变革。