第八代BiCS FLASH已经投入量产,这意味着基于BiCS FLASH的产品也将得到新一轮的升级。新款BiCS FLASH在存储密度和性能方面都有显着提升,尤其是2Tb QLC NAND,是业界最大容量的存储器。

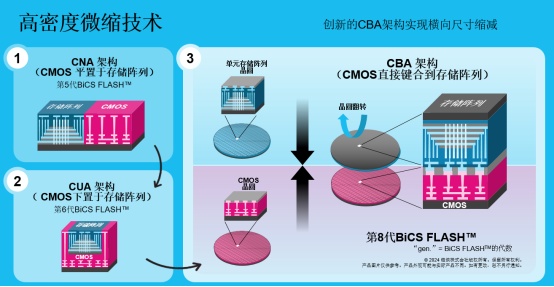

为了让第八代BiCS FLASH突破存储限制,通过专有工艺和创新架构实现了存储芯片垂直和水平扩展之间的平衡。开发的CBA(CMOS to Array,外围电路直接与存储阵列绑定)和3.6Gbps的接口速度,为AI应用、数据中心和移动设备提供了更多潜在的可能性。

技术从来都不是一朝一夕就能实现的。第八代BiCS FLASH突破局限性的背后,是铠侠不断的创新和技术积累。现在第八代BiCS FLASH已经发布,让我们一起来看看第八代BiCS FLASH的厉害之处吧。 。

摆脱高层数字的束缚

与许多芯片制造商推广的工艺技术不再代表晶体管之间的实际距离类似,NAND堆栈层数不再是影响存储容量与占用空间关系的唯一因素。想方设法在单位空间内安装更多的存储单元,打造高密度的存储设备。提高存储密度是最终目标。

在闪存技术从2D向3D转变的过程中,铠侠深切地感受到了这一点。虽然通过布线的小型化提高了每个硅模的存储容量和存储密度,但当布线宽度达到15nm时,设计团队发现了微观世界中更多的问题,例如,每一层晶圆都需要可以做得更薄,堆叠会增加晶圆的高度。为了形成存储单元,需要加工极深且极细的孔,这是不可避免的。进口最先进的设备将花费大量资金。

因此,单纯增加堆叠层数可以在一定程度上解决存储密度问题,但并不是提高存储密度的唯一解决办法。在成本可控的前提下实现高密度、高性能存储成为重要问题之一。通过深度存储、平面方向设计、工艺等各种因素进行优化,横向压缩密度,开发出能够平衡成本和性能的产品。 218层第八代BiCS FLASH就是在这个前提下诞生的。

第八代BiCS FLASH使用的CBA(CMOS to Array)

两块晶圆合二为一

第八代BiCS FLASH遇到的第一个问题是CMOS电路和存储单元晶圆需要不同的处理温度。 CMOS在高温处理过程中会遇到晶体管特性劣化的问题,而存储单元制造则需要高温处理。相应的特征。如何应对CMOS和存储单元不同的温度要求,工程师最终给出的解决方案是CBA(CMOS to Array)架构。

CBA与以前在单晶圆上制造CMOS逻辑电路和存储单元完全不同。而是分成两块单独制造,然后翻转粘贴在一起,这样不同工艺可以发挥更大的优势,进一步压缩生产。时间。

但粘合两个晶圆并不是一件容易的事。为了保证闪存的可靠性,必须以极高的精度进行对准。如果键合直径为300mm的晶圆,精度需要保持在0.003mm以内,否则会导致NAND FLASH无法工作,或者寿命和可靠性降低。

第八代BiCS FLASH 300mm晶圆

因此,在晶圆键合过程中,晶圆表面需要进行高强度的平坦化处理。凭借积累的经验,铠侠能够很好地实现这一点。同时,在存储密度方面,第八代BiCS FLASH也有显着提升。即使NAND层数低于竞争对手,存储密度仍可比竞争对手高出约15%至20%。

第八代BiCS FLASH的电子显微镜成像

图中粉色线代表粘合面。上部是存储单元阵列,下部是CMOS电路。

得益于逻辑电路和结构的优化,第八代BiCS FLASH在提高存储密度的同时也提升了性能,包括写入性能提升20%、读取速度提升10%、功耗降低30% 。 %(写入时),接口速度达到3.6Gbps,接口速度表现也优于同级别产品,从而提高最终产品的性能,如SSD、UFS内存等。

由于第八代BiCS FLASH引入了CBA架构,千兆密度得到了大幅提升。