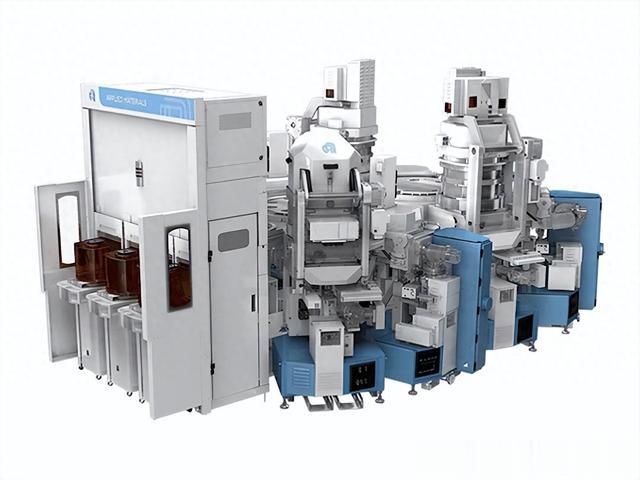

尽管在过去的十年里,摩尔定律的进展显然有所放缓,但每一代新的工艺技术仍在提升晶体管的密度。然而,向更小的晶体管供电面临挑战,因为更小的晶体管意味着芯片内的电源线更细,这增加了它们的电阻,可能导致成品率下降。为了解决这一问题,本周应用材料公司推出了新的Applied Endura Copper Barrier Seed IMS和Volta Ruthenium Copper Vapor Deposition (CVD)工具,使芯片制造商能够在2nm级及更先进的工艺技术中继续使用铜线。

当今先进的逻辑处理器大约有20层金属层,包含细信号线和较粗的电源线。随着晶体管的缩小,缩小布线带来了诸多挑战。较细的布线具有更高的电阻,而较近的布线则增加了电容和电气串扰。两者的结合会导致功耗增加,同时限制性能提升,这对于希望在数据中心处理器中兼顾一切的处理器尤为棘手。将电源轨转移到晶圆的背面预计可以通过减少布线复杂性并腾出更多空间给晶体管,从而提升性能和效率。

然而,背面供电网络(BSPDN)并不能完全解决细线问题。随着光刻缩放的进展,晶体管特征和布线沟槽都变得更小。这意味着障碍层和衬垫在这些沟槽中占据了更多空间,导致没有足够的空间在不产生空隙的情况下沉积铜,从而增加电阻并降低成品率。此外,电线更近也会使低k电介质变薄,使其在蚀刻过程中更容易受损。这种损伤会增加电容,削弱芯片,使其不适合3D堆叠。因此,随着行业的发展,铜布线面临显著的物理缩放挑战,但应用材料公司提出了新的解决方案。

采用二元RuCo 衬垫当代制造技术使用回流焊来填充铜的互连,其中退火过程有助于铜从晶圆表面流入布线沟和通孔。这个过程取决于铜流动的衬里。通常,使用CVD钴膜作为内衬,但这种膜对于3nm级节点来说太厚了(会影响电阻和成品率)。

应用材料公司建议使用厚度低于 20A(2nm,20 埃)的钌钴 (RuCo) 二元衬里,这将为铜回流焊提供更好的表面性能。这最终将允许为无空隙导电铜的回流焊增加 33% 的空间,从而将整体电阻降低 25%。虽然使用新衬垫需要新的工具,但它可以实现更好的互连,这意味着更高的性能、更低的功耗和更高的成品率。

应用材料公司表示,截至目前,其新的Endura Copper Barrier Seed IMS和Volta Ruthenium CVD工具已被所有主要逻辑制造商采用,包括台积电和三星代工的3nm级节点及更先进节点。

台积电执行副总裁兼联席首席运营官Y.J. Mii博士表示:“半导体行业必须大幅提高能效性能,以实现人工智能计算的可持续增长。降低互连电阻的新材料将在半导体行业发挥重要作用,同时其他创新将提高整体系统性能和功耗。

新型低介电常数电介质但是,薄而高效的衬里并不是 3nm 及以后生产节点布线的唯一关键因素。布线沟槽不仅采用 Co/RuCo 衬里和 Ta/N 屏障,还采用低介电常数 (Low-K) 薄膜,以最大限度地减少电荷积聚、降低功耗并降低信号干扰。自 2000 年代初以来,应用材料公司一直提供其 Black Diamond Low-K 薄膜。

但新的生产节点需要更好的电介质,因此本周应用材料公司推出了升级版的Black Diamond材料和等离子增强化学气相沉积(PEVCD)工具,即Producer Black Diamond PECVD系列。这种新材料通过进一步降低介电常数,同时增加芯片的机械强度,使其能够缩放到2nm及更小节点,这对于逻辑和存储的3D堆叠非常有利。应用材料公司表示,新的Black Diamond正被主要逻辑和DRAM芯片制造商迅速采用。

应用材料公司半导体产品事业部总裁Prabu Raja博士表示:“人工智能时代需要更节能的计算,芯片布线和堆叠对性能和功耗至关重要。应用材料公司最新的集成材料解决方案使业界能够将低电阻铜线扩展到新兴的埃米节点,而我们最新的低介电常数介电材料可同时降低电容并增强芯片,将 3D 堆叠提升到新的高度。”

本文由EETOP编译自anandtech