3月31日,国内RISC-V领先厂商睿思芯科在深圳举办2025春季新品发布会,重磅推出,中国首款全自研高性能RISC-V(开放指令架构)服务器芯片——灵羽处理器。

这也标志着高性能RISC-V生态正逐步成型并迈向规模部署阶段。

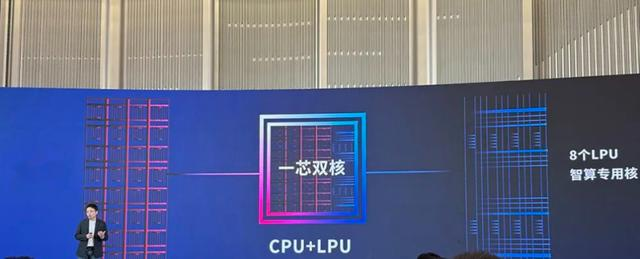

灵羽处理器:全自研、“一芯双核”

灵羽处理器:全自研、“一芯双核”据介绍,据介绍,灵羽处理器基于睿思芯科全自研的CPU核心IP与片上网络IP,计算性能已比肩Intel、AMD等国际主流型号的服务器芯片,推动RISC-V迈入高性能时代。

灵羽处理器采用“一芯双核”的设计架构,由32个高性能通用计算核心(CPU)与8个智算专用核心(LPU)组成,专为DeepSeek等开源大语言模型推理等任务优化。

在内存和I/O接口支持方面,灵羽处理器支持DDR5高速内存,支持PCIe 5.0标准及CXL 2.0协议,并支持高达8路互联。这使其能够满足大模型时代多种新型计算需求,如20盘以上NVMe全闪存储服务器、8卡GPU直连、最高320核高密度算力以及6张400Gbps高性能网卡等。

值得一提的是,目前,灵羽处理器生态体系已集结超50家合作伙伴,涵盖关键器件厂商、整机OEM、系统软件与行业解决方案。另外,灵羽处理器还也完成了广泛软件适配,兼容openKylin、Fedora、Deepin等国产及国际操作系统,支持主流数据库、机器学习框架、虚拟化环境与多租户容器部署等复杂场景。

在发布会现场,联想、长城、三诺等头部合作伙伴,还共同发布了RISC-V高性能解决方案。此外,睿思芯科还与存储头部企业江波龙共同研发了基于灵羽处理器的智能全闪存储系统。另据了解,中国AI龙头商汤科技就是睿思芯科灵羽处理器首批合作客户。

睿思芯科创始人清华本硕毕业,RISC-V原创项目组核心成员之一根据公开信息显示,睿思芯科成立于2018年底,是国内最早做RISC-V指令集芯片的公司之一,创始团队来自于加州大学伯克利分校 RISC-V 原创项目组。2024年,睿思芯科荣获国家级专精特新“小巨人”企业称号。

RISC-V是一个基于精简指令集计算(RISC)原则的开放指令集架构(ISA),它是由加州大学伯克利分校的David Patterson(2017年图灵奖得主)教授团队提出。与专有架构如x86和Arm不同,RISC-V完全开源,并且凭借其简洁性、模块化和可扩展性,被视为新一代高潜力处理器架构。

谭章熹与导师David Patterson(2017图灵奖得主、RISC-V指令架构开创者)

而睿思芯科的创始人谭章熹便是RISC-V指令架构开创者David Patterson教授唯一一位从事体系架构研究的中国大陆学生,在加州大学伯克利分校读博期间深度参与了RISC-V的孵化成长过程,是RISC-V原创项目组核心成员之一,也是现任RISC-V 国际基金会董事。

谭章熹本科就读于清华大学电子工程系,硕士就读于清华计算机系,随后赴加州大学伯克利分校攻读EECS博士。

2017年2月,谭章熹于美国硅谷创立 OURS 公司,开展基于 RISC-V 的 CPU 开发工作。

2018年8月,谭章熹归国,在深圳创立睿思芯科公司,致力于用最先进的RISC-V 处理器技术和产品服务中国广大行业用户。

自创立以来,睿思芯科便获得了多家顶级投资机构背书,截至2022年底已完成多轮融资,股东包括北极光创投、字节跳动、高瓴创投、翼朴资本、联想创投、百度风投、水木投资集团、真格基金等。睿思芯科中国总部位于深圳,在成都等地设有多个办公室。

作为中国最早做RISC-V指令集芯片的公司之一,睿思芯科的创始团队经过7年的奋斗,已研发出多款高能效、高性能的处理器产品,并与世界500强中的多家芯片核心头部厂商合作落地,为其提供IP授权和SoC定制化开发合作。

目前睿思芯科拥有37项,RISC-V领域发明专利,涵盖超标量向量融合架构、异构互联技术、动态功耗管理等核心领域。

由于X86和ARM架构的长期垄断,RISC-V架构成为了很多芯片厂商未来的发展方向。中国工程院院士倪光南就曾指出,目前CPU市场主要被x86和Arm架构所垄断,而中国想要打破这个局面,实现自主可控,开源的RISC-V架构将是一大机遇和发展方向。

在算力需求持续增长的背景下,灵羽处理器作为RISC-V架构的国产高性能代表,正迎来广阔市场空间。有望以其高能效、高灵活性与完善生态适配的全国产计算方案,成为新一轮国产创新的重要推动力量。